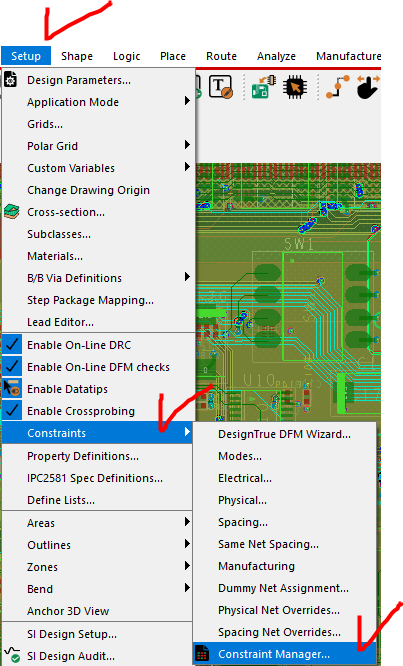

고속 PCB를 설계할 때, 특정 고속 주파수가 필요로 하는 Net의 신호 손실 및 왜곡을 줄이기 위해 Via사용을 최소화 해야 한다. Allegro PCB 라이센스가 있으면 Electrical Constraint Rule에서 Via 갯수 제한을 설정할 수 있다.

(Contraint Manager 사용 방법은 아래 참고)

https://ansan-survivor.tistory.com/1111

[PCB Editor] OrCAD PCB / Allegro PCB Constraint Manager Rule에 대해서... (CM Rule에 대한 사용법)

OrCAD PCB 또는 Allegro PCB에서 무조건 사용되는 Constraint Manager이지만, 제대로 사용방법을 이해하고 사용하는 사람이 드물기도 하고, 또 이 때문에 진입장벽이 있다. 또 아주 디테일한 Rule설정은 OrCAD

ansan-survivor.tistory.com

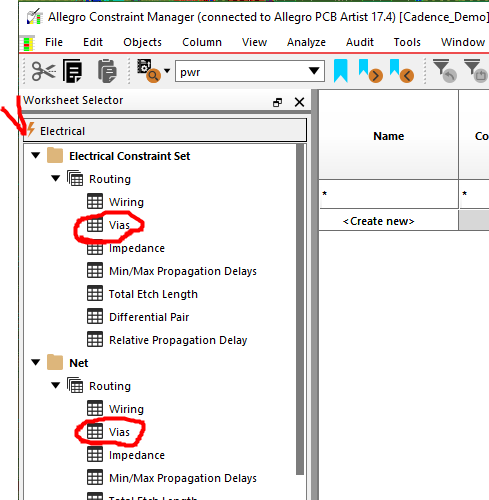

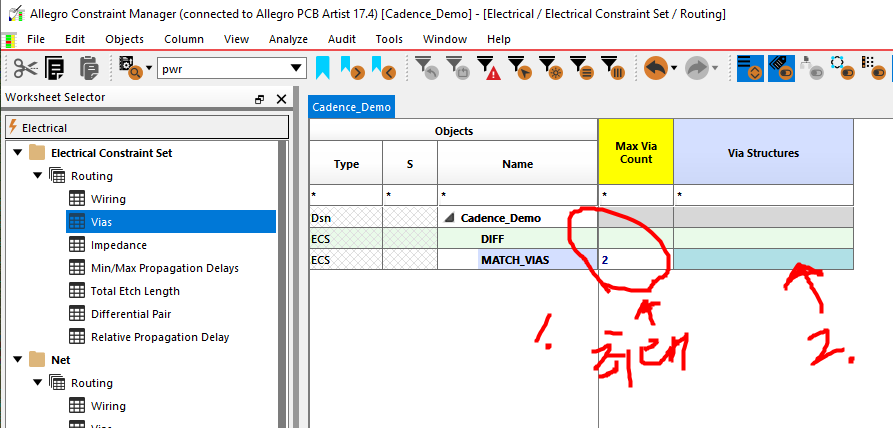

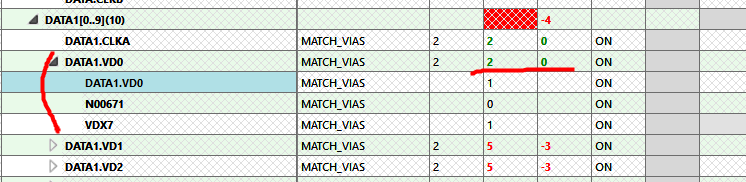

1. Constraint Manager Electrical Rule Vias 항목

2. Rule 설정

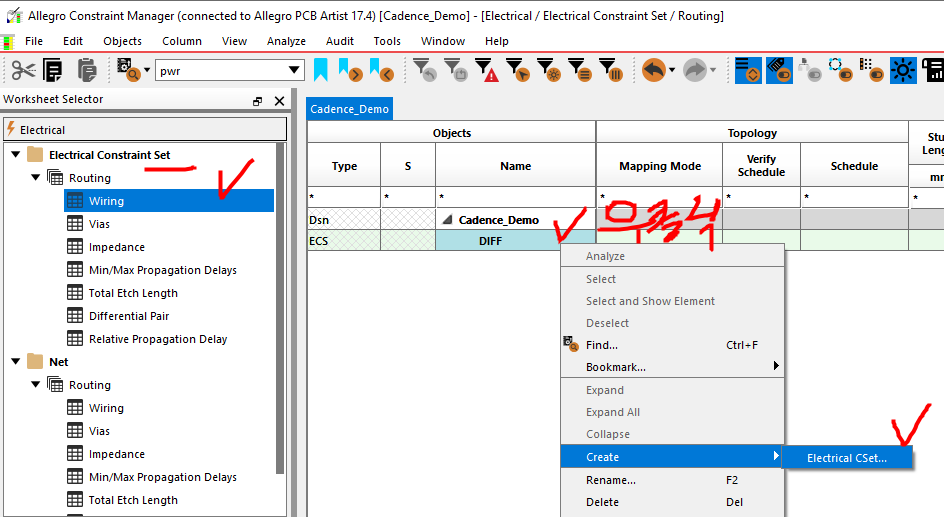

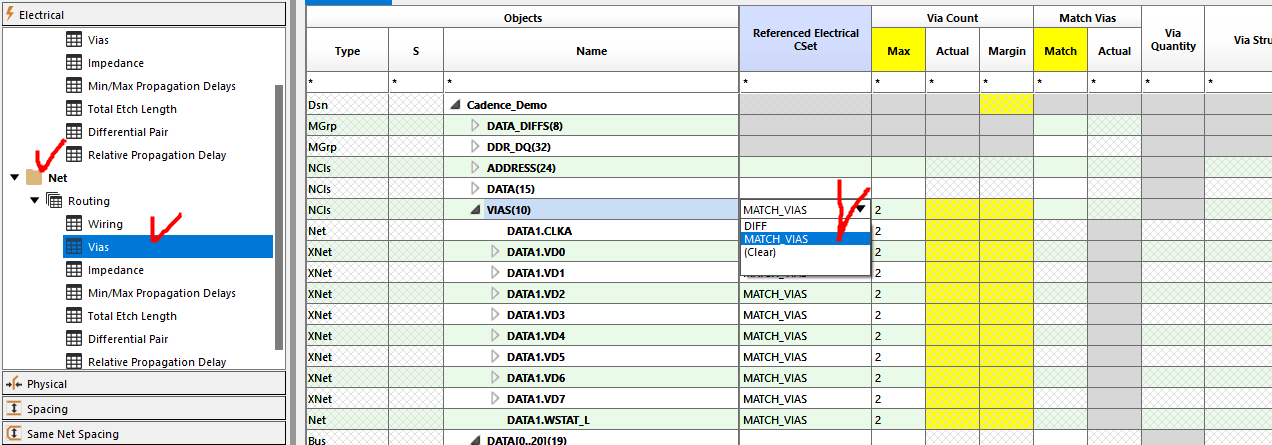

Constraint에는 Set을 만들어 적용하는 방법이 있고, 각 개별 Net에 바로 적용하는 방법이 있다.

여기서는 Set을 만들어서 하위 Net에 적용시키는 방법 사용.

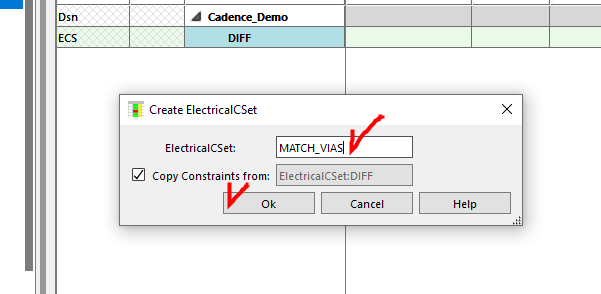

2-1. Class생성 및 Set 값 설정

(Via Structure의 사용방법은 아래 참고)

https://ansan-survivor.tistory.com/212

[PCB Editor] OrCAD PCB Via structure기능 사용하기

Via의 일정한 형태의 모양을 .xml 파일로 저장하여 반복되는 작업을 편리하게 사용할 수 있도록 한다. 이 옵션은 모든 라이센스에서 가능하다. 아래와 같인 BGA Fanout을 엄청나게 많은 핀들에 적용

ansan-survivor.tistory.com

2-2. Set한 설정을 Net에 적용. (아래에서는 다발로 묶인 여러 bus net에 한방에 적용)

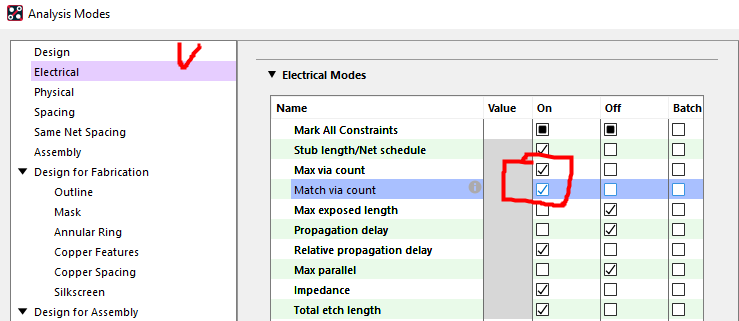

3. 해당 Electrical Via Mode를 On 시켜준다.

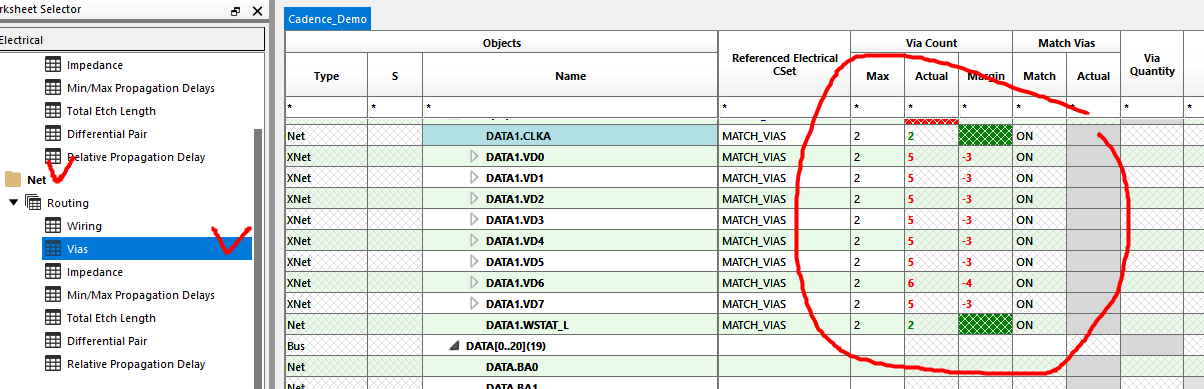

그러면 이제 Rule에 부합하는지 판독이 되며, 초록색은 합격, 빨간색을 불합격이며 Max 2로 되어있는데, 실제 (Actual) 5개로 초과되었으니 이제 설계자가 수정하여 Rule에 부합하도록 해서 PASS를 만들어야 한다.

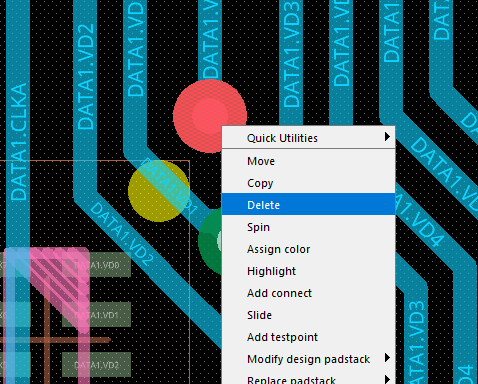

4. 수정해서 부합시키기

더블클릭하면 해당 Net가 하이라이트되어 이동된다.

아래영상참고

https://www.youtube.com/watch?v=ilLkFKT2R1U