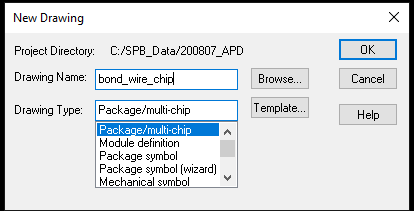

1. File - New해서 새로운 디렉터리 지정

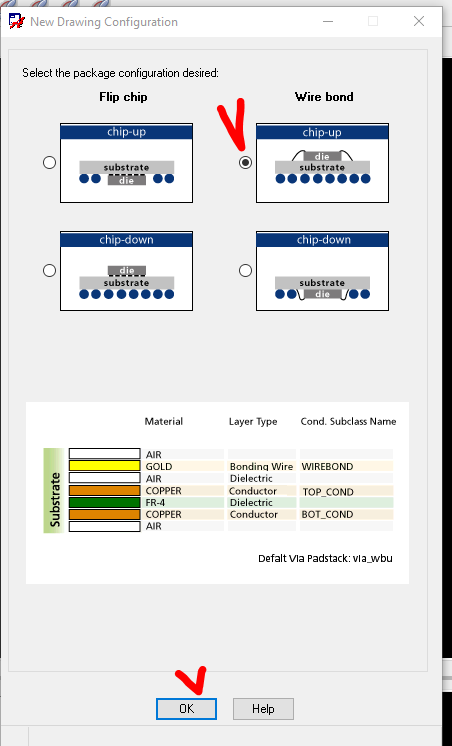

2. 만들 모양 보고 선택 (wire bond타입, BGA핀을 아래로)

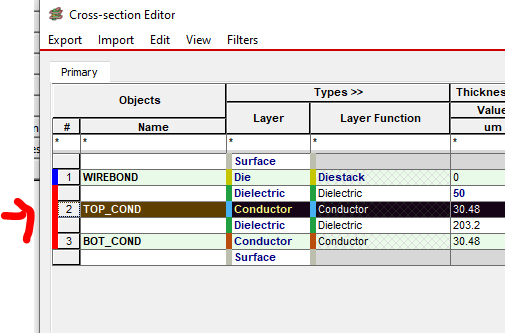

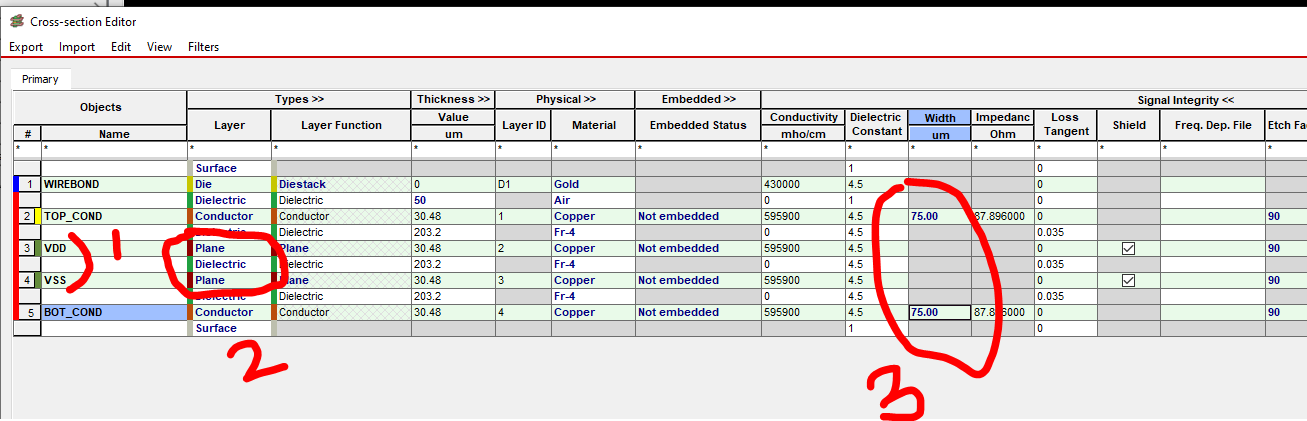

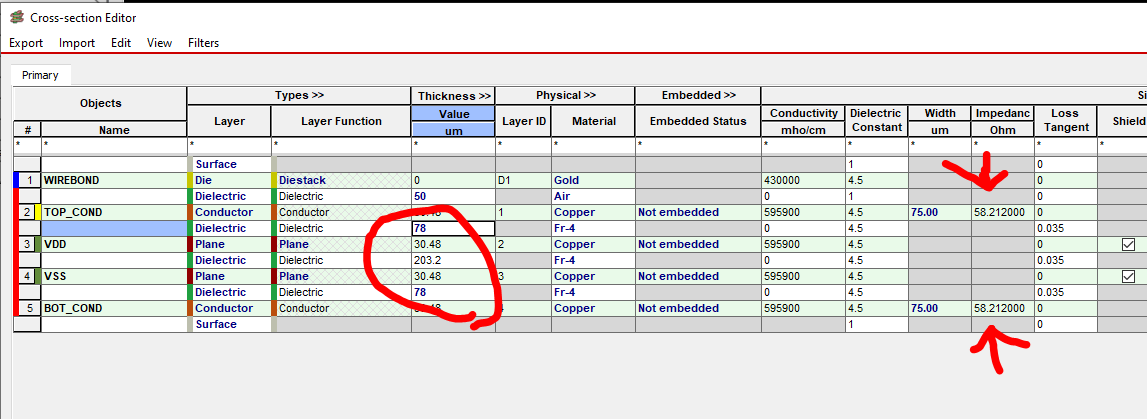

3. Cross-Section 설정 (Layer 설정, layer 두께, Trace의 두께 타켓 임피던스 설정)

Top과 Bottom사이 VDD VSS추가

VDD와 VSS layer추가, Plane으로 변경

Trace의 Width 값을 75로 변경하면 임피던스 값이 자동으로 변경된다. (단 인접 Layer에 반드시 Reference Plane 있을것)

reference plane과의 높이를 설정하여 impedance가 58.xxx 로 계산됨.

임피던스를 바꾸는 요인은 Reference Plane과의 거리(h), Trace의 폭(W), 유전율(E) 임으로...

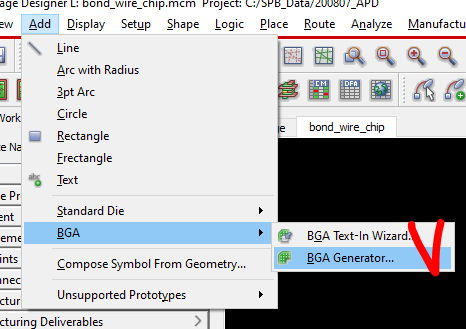

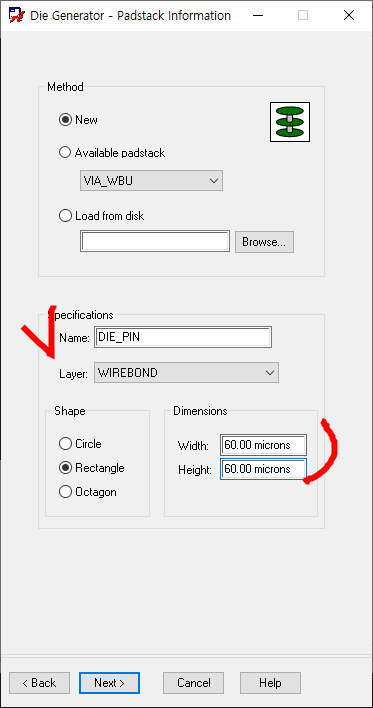

4. BGA핀 생성하기 (BGA Generator)

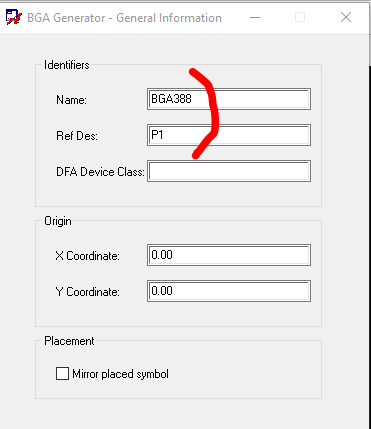

이름과 Ref를 지정

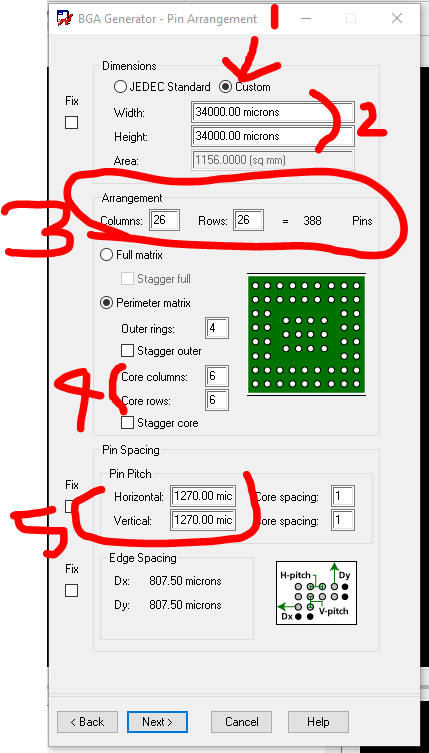

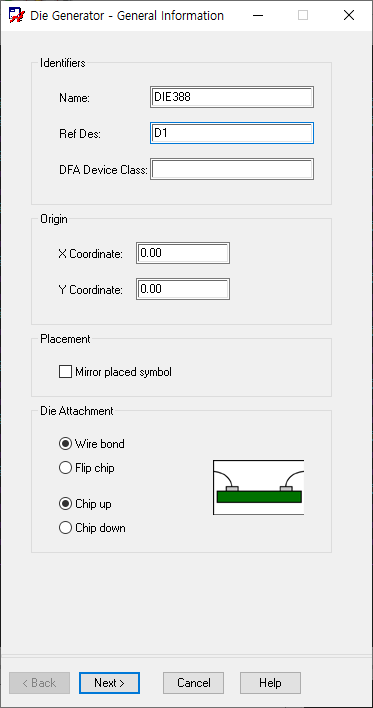

사용자 정의 제작 - 가로 세로 길이 - 외곽선 핀 갯수 - Core(내부 사각형) 핀쌍 - 핀 pitch( micro 단위)

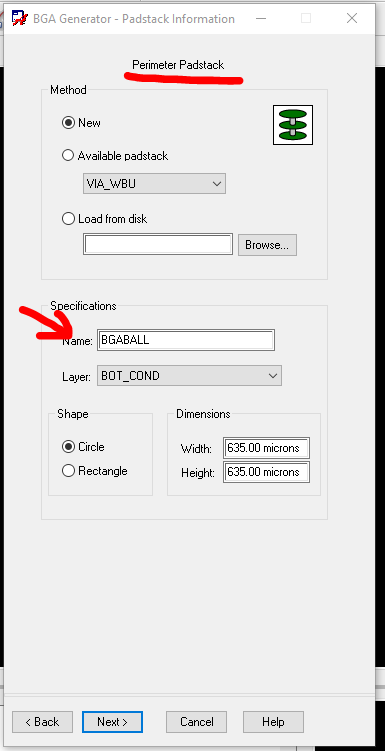

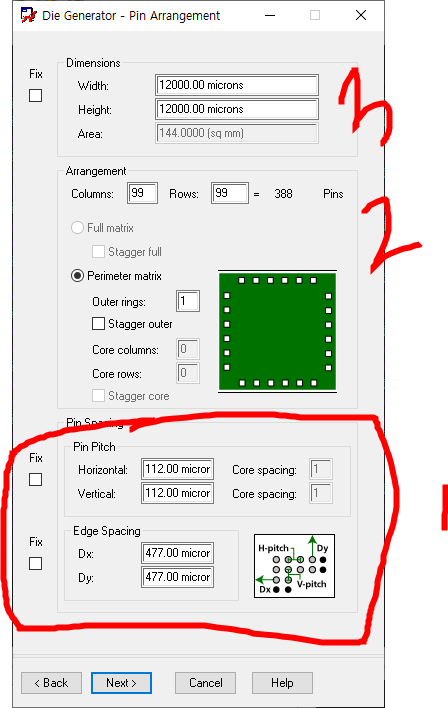

외곽(Perimeter) 를 위한 핀 설정, Layer는 Bottom부분에

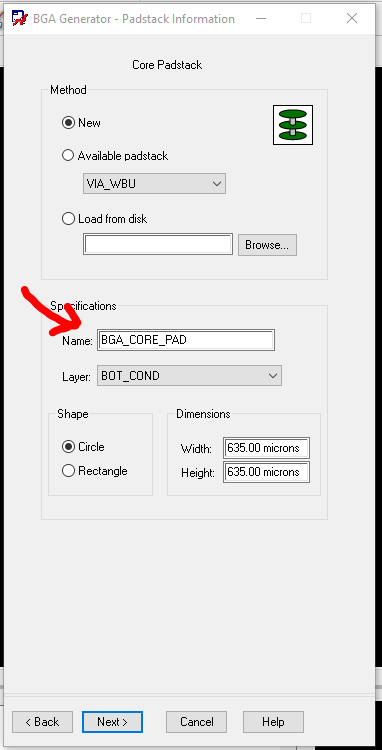

내곽(Core) 를 위한 핀 설정 (핀pad명이 다르게)

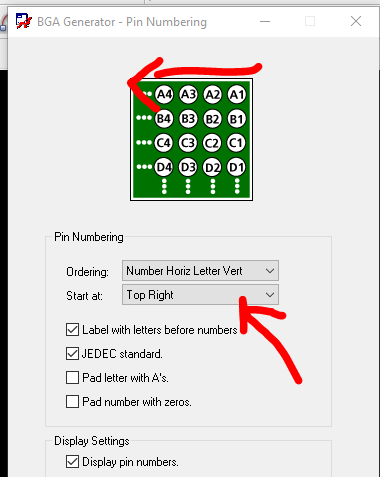

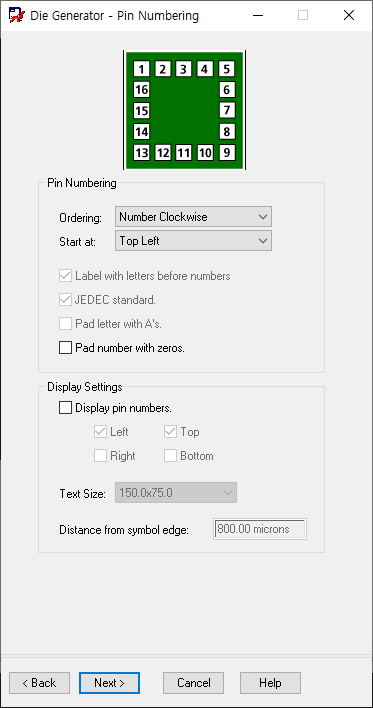

핀번호 오른쪽 상단을 첫번째로 시작

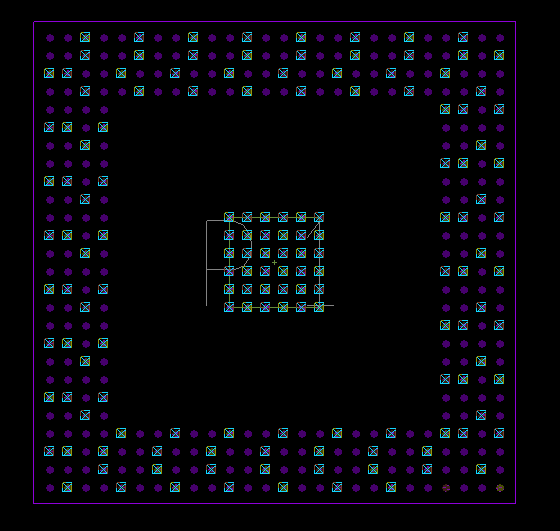

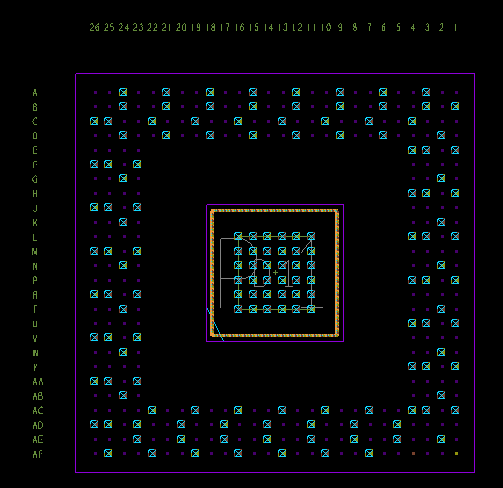

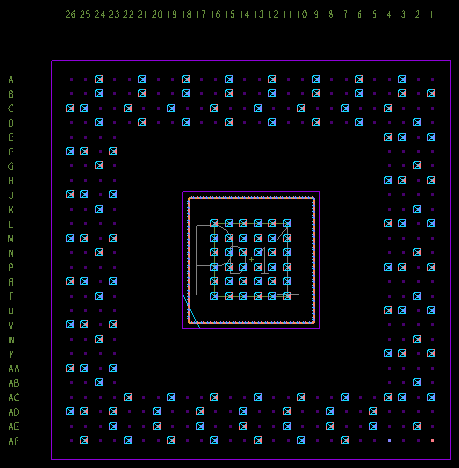

BGA 배치 완료,

*그러나 Net는 오직 VSS와 VDD만 만들었으므로, 저 사각박스를 제와한 나머지 핀은 dummy net이다.

5. Die 배치 시키기

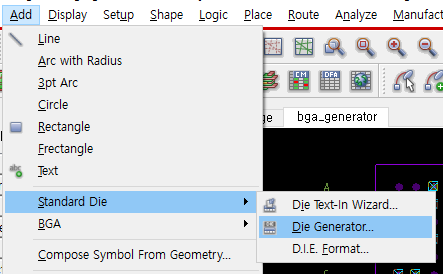

Add - Standard Die - Die Generator

아래 순으로 수정

Die가 어디부터 시작될지 설정 (default로 진행)

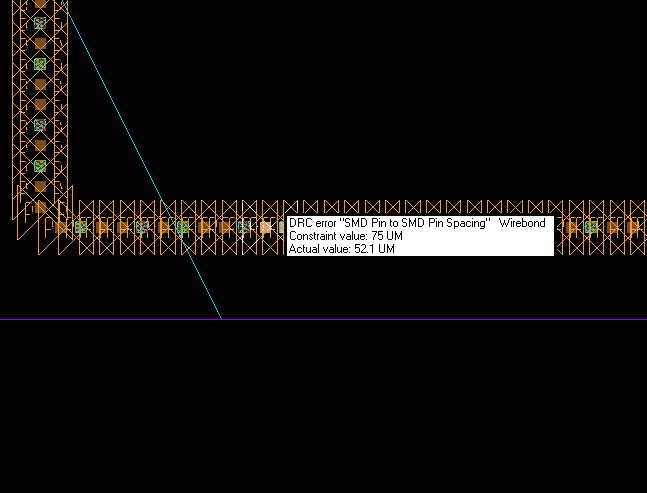

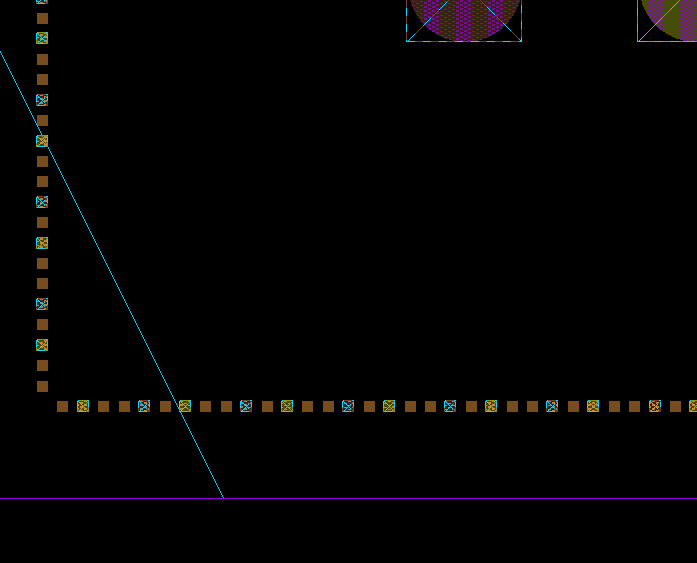

Perimeter BGA핀과 Core BGA핀 사이에 Die가 생성되었으나, 아래와 같이 DRC에러 마크가 쫙 뜨게된다.

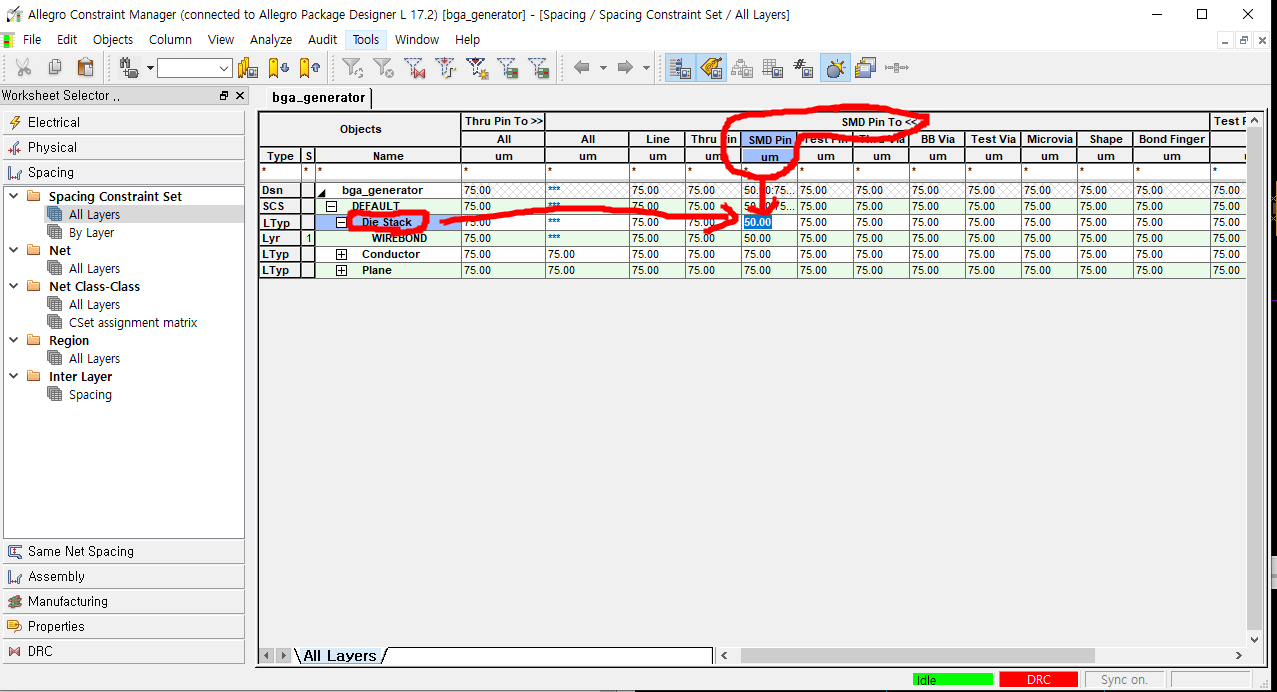

6. Constraint Rule 수정하기 (DRC에러 조정)

에러사항이 die핀의 smd to smd spacing이므로 아래와 같이 수정한다.

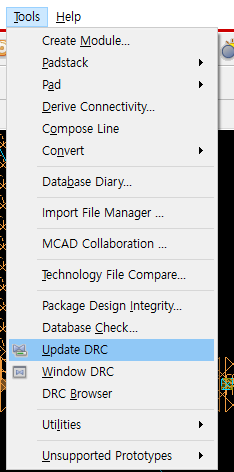

tools - update DRC 해주면, 위에 적용한 Rule로 다시 DRC를 체크한다.

DRC마커가 사라졌다.

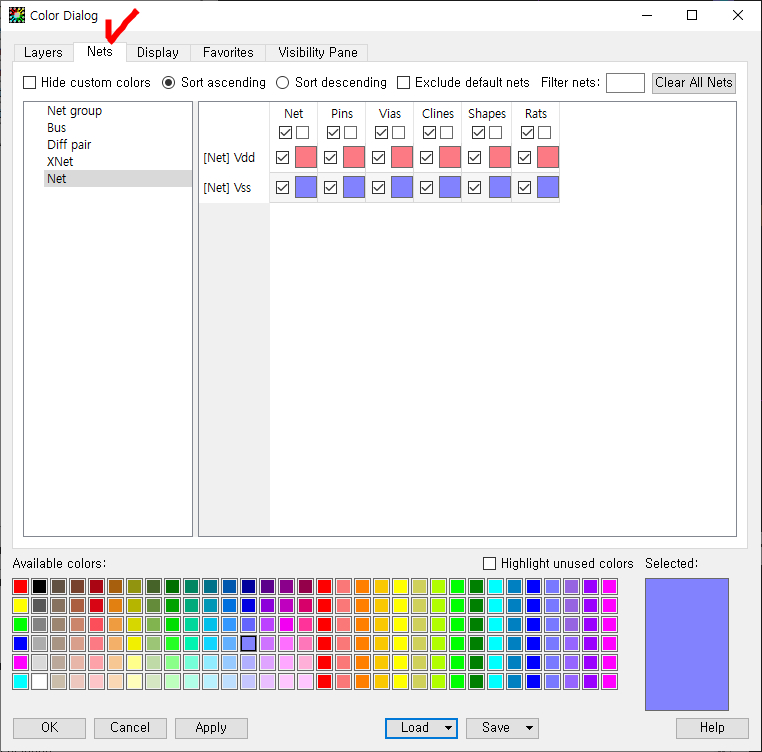

6. Pin Color 설정 (VDD, VSS 알아보기 쉽게)

아래 같이 BGA핀과 Die가 모두 배정되었다.

(패키지 설계 용 via만드는 방법 아래 참고.)

https://ansan-survivor.tistory.com/268

[Allegro Package Designer] Wire Bond(와이어 본드) 타입 via만들기

1. 단위 Micron 변경 2. Drill 사이즈, 200 마이크로미터 3. 심볼 설정 4. Layer별 pad설정

ansan-survivor.tistory.com