Cadence에서는 Allegro PCB 및 IC 의 커스터마이징을 위한 SKILL이라는 언어를 지원하고 있다.

각종 내장된 함수로 여러 기능들을 입맛에 맞게 커스터마이징을 시킬 때 사용하는 SKILL언어에 대한 사용법이다.

(아래 참고)

https://ansan-survivor.tistory.com/152

[Cadence Allegro SKILL] 언어 사용법 및 기초, SKILL파일 불러오기

Cadence Allegro PCB Editor에서는 SKILL이라는 언어를 제공하여 기능을 사용할 수 있다. 이를 활용해본다. SKILL에서는 띄어쓰기(Space) 구분자가 중요함으로 이를 각별히 주의한다. Allegro PCB Editor에서 SKIL..

ansan-survivor.tistory.com

RAVEL = (Relational Algebraic Verification Extension Language)

아래 문서는 Cadence의 RAVEL이라는 언어에 대한 소개 자료이다.

RAVEL언어는 역시 상업용언어이며, 라이센스를 구매해야 사용이 가능하다.

Cadence RAVEL Relational DRC System Solution for PCB and SIP For Cadence Allegro Users

With constant pressure to reduce time to market and with fewer resources, you need to maximize the productivity of your package and PCB design environments.

Provided as a Virtual Integrated Computer-Aided Design (VCAD) Productivity Package, Cadence® RAVEL significantly optimizes and improves the design rule checks (DRCs) performed on the PCB or system-in-package (SiP) design databases to meet frequently changing requirements of design quality and manufacturing processes.

A mature and proven tool available today, RAVEL can help you close the gap between the commonly available and custom DRCs required to achieve 100% design rule coverage.

시장 출시에 대한 시간적 압박을 받고 있는 상황에서 리소스의 낭비를 최소화 시켜야 한다. 이를 위해서 PCB나 Package의 설계에 대한 생산성을 극대화 시켜야 한다.

VCAD(Virtual Integrated Computer-Aided Design) Productivity Package로 제공받는 Cadence® RAVEL은 잦은 설계 변경 요청, 제조 프로세스의 변경 요청에 대한 PCB나 System-in-Package(SiP)의 데이터베이스의 Design Rule Check (DRC)를 체크하는데 최적화 되고 발달되어있다.

많이 향상되고 그 효율이 증명된 RAVEL은 Design rule에서 100%로 만족시켜야 하는 Custom DRC와 공통적으로 만족해야 하는 DRC와의 격차를 줄일 수 있다.

RAVEL Relational DRC System

The Relational Algebraic Verification Extension Language (RAVEL) enables PCB and SiP designers to rapidly develop custom DRCs on demand, utilizing current design rule manuals (DRMs).

This leads to an automated and drastically reduced DRC implementation effort.

Key Features:

• Enables definition of custom PCB and SiP manufacturing and assembly DRCs

• DRCs performed on PCB or SiP design database

– Manufacturing data export is not required

– DRC violation markers created directly on design database objects

• Based on RAVEL language for coding of design rules

– Optimized for expressing PCB and SiP design rules

– Independent of SPB version and Cadence® Allegro® PCB/SiP layout design database

• Compilation and encryption of DRC source code for IP protection

• Interactive DRC execution

– Integration of custom DRC in Allegro Constraint Manager

– Distribution of encrypted custom DRC through Allegro Constraint Manager files

• Batch DRC execution

– Distribution of encrypted custom DRC through batch DRC file

– Support for run-time DRC and constraint value selection, customizable reports

RAVEL(Relational Algebraic Verification Extension Language)을 사용하면 PCB 및 SiP 설계자가 DRM(Design Rule Manual)을 활용하여 커스텀 DRC를 필요에 따라 빠르게 개발할 수 있습니다.

특징 :

• 커스텀 PCB 또는 SiP manufacturing 이나 assembly DRCs 정의 가능

• PCB 또는 SiP 설계 데이터베이스로 DRC 수행

– Manufacturing 데이터 Export가 필요 치 않음

– 설계 데이터베이스 Object에 바로 DRC 마커 생성

• RAVEL기반 언어로 Rule 코딩 작성

– PCB 또는 SiP 설계 Rule에 최적화

– SPB version이나 Cadence® Allegro® PCB/SiP 데이터베이스에 영향이 없음 (독립적 실행 가능)

• IP보호 차원으로 DRC 소스 코드 암호화

• Interactive DRC execution (대화형 DRC 실행)

– DRC in Allegro Constraint Manager 내 커스텀 DRC로 통합되어 있음

– Allegro Constraint Manager 파일을 통해 암호화 시킨 커스텀 DRC 배포

• Batch DRC execution (Batch형 DRC 실행)

– 배치파일(batch file)로 암호화된 커스텀 DRC 배포

– 커스텀 리포트, Constraint 값 선택, Run-Time DRC 지원

Benefits (이점)

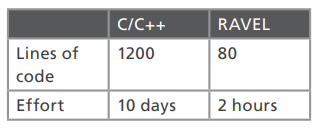

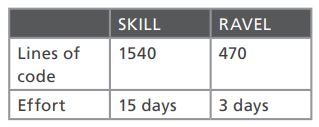

Key advantages of RAVEL are:

• Reduced DRC implementation effort

– RAVEL DRC language is specialized for expressing design rules in PCB and SiP

– Does not require knowledge of SKILL or C/C++ programming languages

– Does not require knowledge of Allegro PCB/SiP database

• Reduced DRC maintenance effort

– RAVEL rules are independent of database

– RAVEL rules are independent of SPB software release

– All dependencies are built into RAVEL DRC engine

RAVEL 핵심적인 이점:

• DRC를 지정하는 노가다 감소

– RAVEL DRC 언어는 PCB 이나 SiP에 특화된 design rule 사용

– SKILL 이나 C/C++ 프로그래밍 지식이 필요 없음

– Allegro PCB/SiP 데이터 베이스 구조에 대한 이해가 필요 없음

• DRC를 유지 보수하는 노가다 감소

– RAVEL rule은 데이터베이스에 독립적

– RAVEL rule은 SPB 버전에 독립적

– 모든 종속성은 RAVEL DRC 엔진을 통해서만 내장되어 있음

Rule 수행 플로우

RAVEL DRC Application Examples (RAVEL DRC 적용 예)

Thickness-Dependent Die Overhang

DESIGN RULE:

Maximum overhang dmax of the edge of the wirebond die over the edge of the component (die or spacer) directly underneath, with dependence on the thickness t of the die

dmax(t > 80) = 400

dmax(40 < t ≤ 80) = 200

dmax(t ≤ 40) = 100

두께에 따른 Die의 돌출

DESIGN RULE:

Die의 t값(두께)에 따라 달라지는 Wirebond이 되어있는 Die 가장자리와 바로 아래 있는 Component (Die 또는 Spacer)의 가장자리의 최대 돌출 변수 값 "dmax"

dmax(t > 80) = 400

dmax(40 < t ≤ 80) = 200

dmax(t ≤ 40) = 100

(참고할만한 사이트 - Cadence RAVEL 영문 인강)

https://www.cadence.com/en_US/home/training/all-courses/86217.html

Advanced Design Verification with the RAVEL Programming Language

Length : 2 days This course introduces you to the RAVEL programming language. RAVEL, Relational Algebra Verification Expression Language, is a language to implement System in Package and PCB design rules. RAVEL enables PCB and SiP designers to rapidly deve

www.cadence.com