High speed(고속신호)전송 관련하여 PCB 배선(라우팅)을 하게 되면, Return path의 경로를 최대한 짧게 해주는게 중요하다. 자세한 내용은 아래 참조.

https://ansan-survivor.tistory.com/57

고속신호 PCB설계시 리턴패스(Return Path) 고려

고속신호에서 설계할 때, Return Path가 어떻게 되냐에 따라 노이즈와 신호무결성이 보장된다. 그로인해 Ground설계를 조심스럽게 해야 하는데, 고속 Trace아래 반드시 Return path를 위한 GND plate가 따라�

ansan-survivor.tistory.com

이 기능은 Allegro PCB Editor의 High speed Option이 있어야 가능하다.

관련 Rule을 빠르게 설정하여 설계를 진행할 수 있다.

아래 동영상을 참조하여 포스팅을 만들었다.

https://www.youtube.com/watch?v=tx7ms7nSRUM

먼저 일부러 Return path를 방해하기 위해 GND plane에 void를 만들어 주었다.

void를 만드는 방법은 아래 참고.

https://ansan-survivor.tistory.com/102

[PCB Editor] Cadence OrCAD PCB Editor Shape(plane) 빈공간(Void) 넣기.

OrCAD PCB Shape (plane)에 Void(빈공간) 넣기 1. 모든 Shape 수정은 Shape Edit 모드로 한다. Shape 모드로 바꾸는 방법은 2가지가 있다. 2. Find 옵션에 Shapes를 체크하여 활성화 한다 (Shape만 선택 가능하도..

ansan-survivor.tistory.com

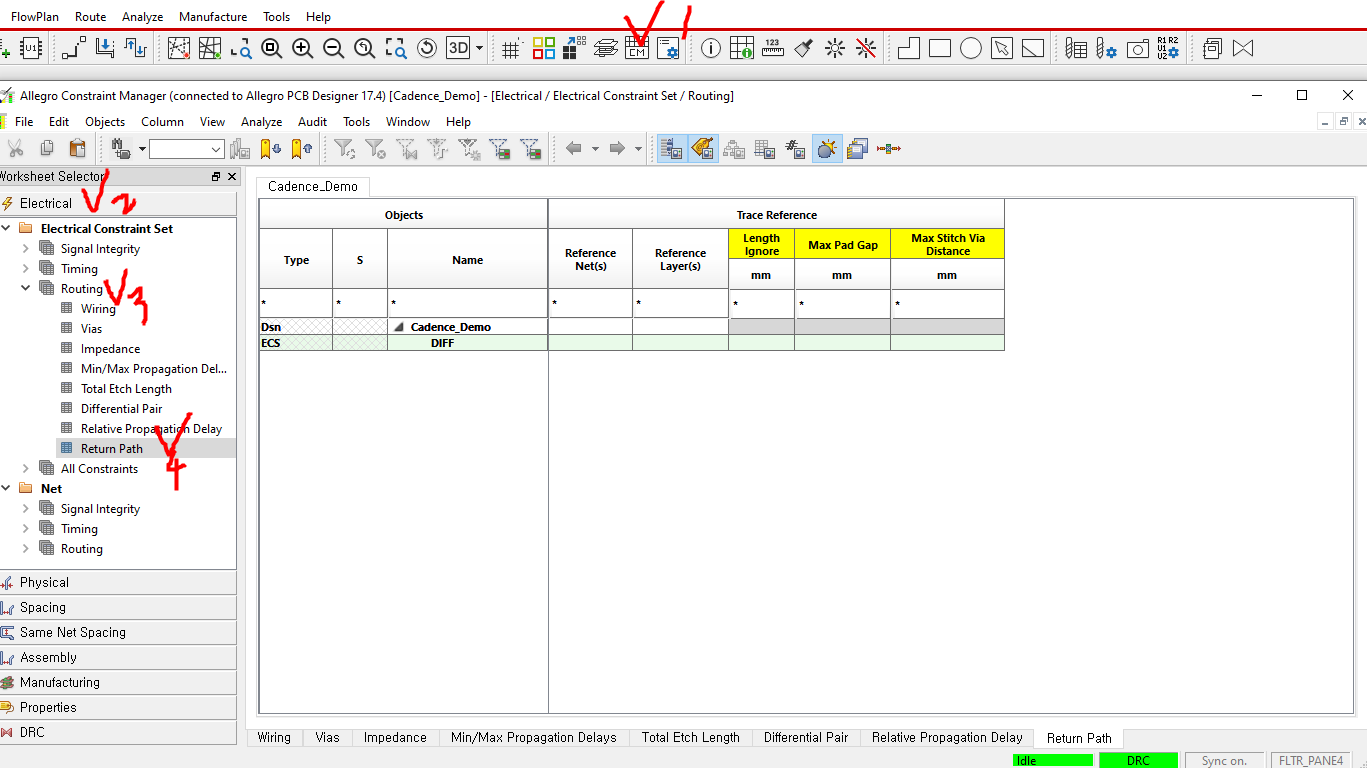

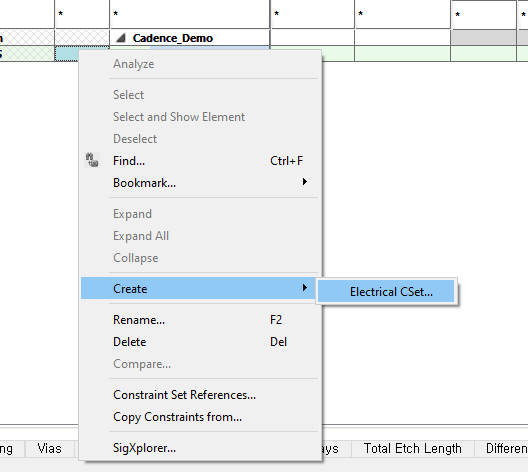

1. CM Rule - Electrical - Routing - Return Path

0(GND plane)을 기준으로

Cloest Plane : 가장 가까운 plane

Length Ignore : 0.5mm 정도는 허용해줌

Max pad Gap : 0.6mm 이 초과는 안됨.

2. 설정한 Set을 Net에 부여함. (아래 Net에 부여함 - DATA.BD0 ~ BD6)

3. 설정한 CM룰을 사용하겠다고 설정함.

4. DRC 체크를 갱신함. (업데이트)

5. 해당 layer만 선택적으로 확인함. (GND와 고속신호).

DRC에러가 발생함을 알 수 있다.

6. CM룰 적용 테스트

해당 DRC를 보면, 0.5mm 이내에 plane과 있어야 한다고 함.

이를 움직여 0.5mm 이내로 수정하면 DRC가 사라짐.

위 설정한 부분을 직관적으로 볼 수 있도록하는 기능이 있다.

아래 참조

https://ansan-survivor.tistory.com/208

[PCB Editor] Allegro PCB Designer, High speed option, Vision Manager 사용하기

아래 작업은 이전포스팅의 Return Path를 바탕으로 만들어서 Vision Manager를 적용해보았다. https://ansan-survivor.tistory.com/207 [PCB Editor] Allegro PCB Editor High speed Option, Return path Constrai..

ansan-survivor.tistory.com