Differential Pair에 대해..

(위키 참고)

https://ko.vvikipedla.com/wiki/Differential_signaling

<< 신호의 직렬화 고속화 >>

<< 높은 신뢰도의 신호 전달 >>

<< 노이즈 영향이 적어 저전압으로 사용에 용이 >>

<< Common Mode Noise에 강함 (전자파 저항성 상승) >>

<< Differntial Pair Naming Convention >>

<< Differntial Pair Signal Delay>>

<< 신호의 직렬화 고속화 >>

최근의 대부분 신호는 보통 직렬의 연결방식(serial signal communication)을 많이 사용한다. 이 방식이 병렬방식보다 많은 이점이 있기 때문이다. 병렬의 한 포트는 하나의 신호만 보내게 되는데, 반면 직렬의 신호는 1과 0의 디지털 신호로 빠르게 여러정보를 전달 할 수 있다. 따라서 Connector의 크기를 획기적으로 작게 만들 수 있다.

이제는 위에 Serial 커넥터보다 더 작고 빠르게 포트가 진화했다. 대표적으로 USB를 예를 들수있다.

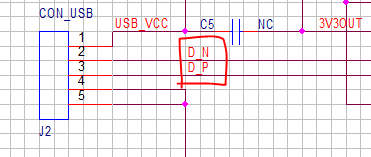

USB는 오직 D+와 D-로 신호를 전달한다.

실제 PCB보드에서는 이 USB의 전송선로는 아래와 같이 Differential Pair의 Pattern을 볼 수 있을 것이다.

또한 여러 고속 신호선(HDMI, CAN 등등)에도 사용되고 있다.

<< 높은 신뢰도의 신호 전달 >>

Differential Pair의 강점으로는 외부 노이즈에 강하다.

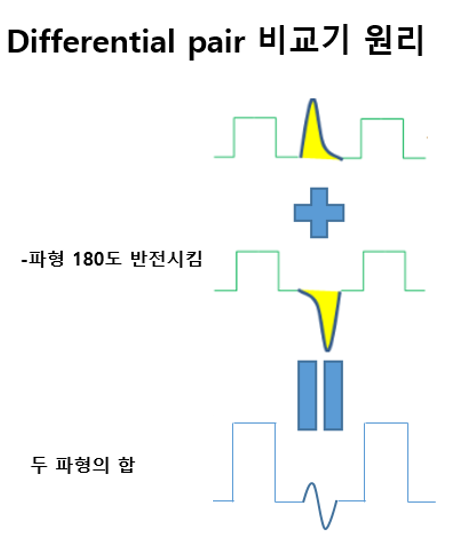

아래 그림을 참고해면,

예를 들어 Sender가 디지털 신호 010010 을 보내면, Reciver에도 010010 이 도착해야 한다.

Sender측에서는 Inverter를 통해 하나는 반대되는 신호를 보낸다. 즉, 서로 상반되는 디지털 파형을 Diff Pair를 통해 전달

그러나 만약 외부에서 전기적 노이즈가 발생하여 파형이 위에 노란색으로 표시된 것처럼 변화되었다고 보자,

그러면 신호기준선을 넘어 파형은 아마도 010110 또는 011110 과 같이 원래 신호가 아닌 다른 신호가 되어 전달이 될 수 있다.

그래서 마지막에 있는 비교기를 통해 서로 같은 파형은 제거하고, 파형이 상반된 부분만 남겨두고 통과를 하게된다.

하지만 약간의 흔적이 남아있지만(Reciver 쪽 파형) 신호기준선보다 아래로 낮아지므로, 디지털 신호에서는 이를 0으로 인식하여 원래 보내고자 했던 010010이 정상적으로 보내짐을 알 수 있다.

Reciver(RX)에서는 두 포트 D+, D-가 연결되어있다.

비교기(Reciver)는 1개의 전송선로 (D-)의 위상을 180도 바꾸어서 그 다른 한 파형(D+)과 더해준다.

그러면 노이즈는 상쇄되어 사라지게 되고, 보내고자 하는 신호는 더 강하게 나타난다. 그러면 원래 보내고자 하는 신호만 남게된다.

아래는 예시로 비교기에서 어떻게 파형에서 노이즈를 제거하는지 보기 좋게 그렸다.

또한, 어떠한 노이즈에도 잘 견디기 때문에, 저전압으로 사용하기에 용이하다.

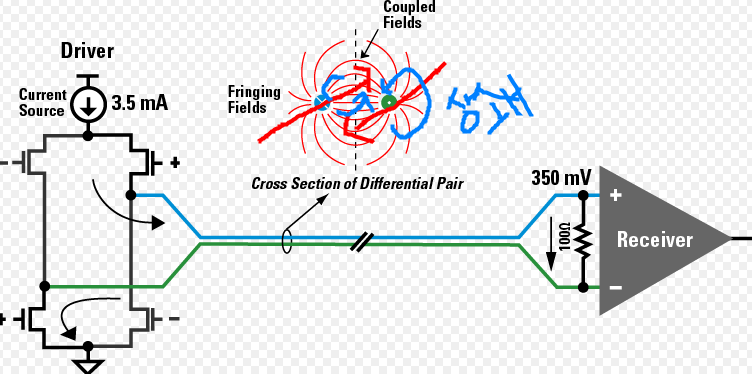

<< Common Mode Noise에 강함 (전자파 저항성 상승) >>

아래 그림에서 D+와 D-의 전류는 서로 반대방향으로 움직인다. 전류가 흐를 때 발생하는 자기장이 오른손법칙에 의해 서로 반대방향으로 작용하여 상쇄가 된다. 상쇄되는 자기장으로 인해 더이상 전자파가 발생하지 않을 뿐만 아니라, 외부에서 오는 전자파의 영향도 줄어든다.

즉, EMI/EMC의 성능도 향상된다.

<< Differntial Pair Naming Convention >>

보통 회로 설계상(Schematic)에서 Differential Pair임을 표시할 때, 아래와 같이 두 wire가 함께 지나가며 Net이름 뒷부분에 _N(-)과 _P(+) 를 함께 붙인다. Net의 이름으로만으로 Differential Pair임을 짐작할 수 있다.

<< Differntial Pair Signal Delay>>

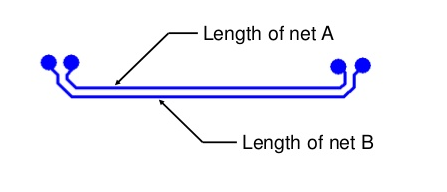

아래의 경우 서로의 길이가 다르다.

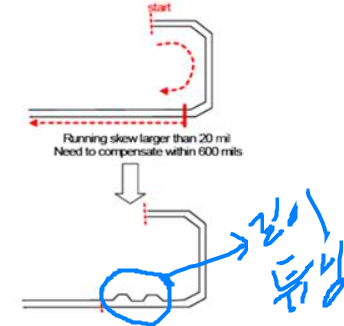

Differential Pair에 보내지는 신호는 서로 Phase(위상)가 맞아야 한다. 그러나 Phase가 맞지 않을 경우에는 D+와 D-의 길이(Length)를 조절해서 맞춰야 한다. 아래 그림을 참고해보자.

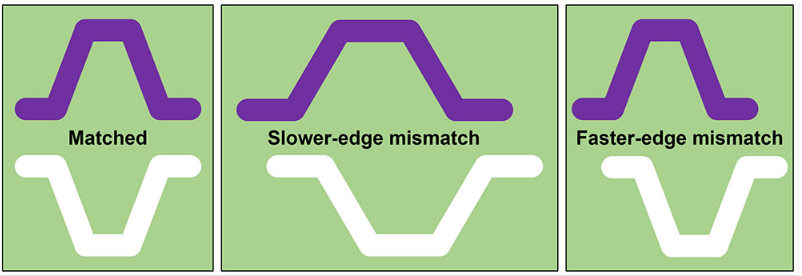

신호가 Matched되어 도착해야 하는데, 서로 Phase가 달라 Slower-dege mismatch(약간 벗어남), Faster-edge mismatch(많이 벗어남) 이 발생할 수 있다.

이경우 아래와 같이 길이를 튜닝하면서 Phase가 Match되도록 만들어 주어야 한다.

아래는 OrCAD / Allegro PCB의 Differential Pair의 길이를 조절하는 부분이다.

https://ansan-survivor.tistory.com/531

[PCB Editor] OrCAD PCB Differential Pair의 Dynamic Phase 사용하기 (디퍼런셜 페어 양단의 길이를 최대한 일치

이 기능은 OrCAD Professional 이상 또는 Allegro 라이센스에서 가능하다. Differntial Pair에 대해서 아래 참고 ansan-survivor.tistory.com/21 PCB Differential Pair에 관하여 실제 PCB의 고속 신호선(USB, CAN..

ansan-survivor.tistory.com

=======================================================================

** Differential Pair 설계시 Tip**

- Differential Pair는 가능한 최단거리의 Trace 길이로 설계한다.

- Differential Pair를 최단거리로 바꾸기 위해 가능하다면 부품배치(Placement) 자체를 바꾸는 것도 좋다.

- Differential Pair는 가능한 Coupling을 유지한다. (양쪽이 거울에 비치는것 처럼 동일 간격유지)

- Differential Pair는 가능한 Via를 배치하지 않는다.

- Differential Pair에 Via가 필요하다면, Via근처에 GND via를 배치한다. (이때 GND via의 간격도 동일해야 한다)

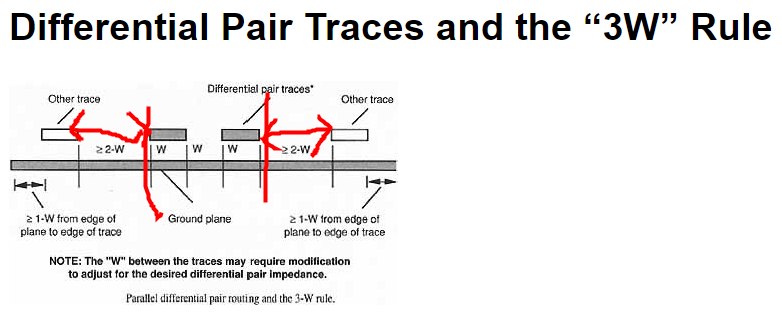

- 3W법칙을 지키며 설계한다. ( Trace Width(W) 의 3W 간격을 유지해야 원치않는 cross-talk방지 )

( Copper Plane도 마찬가지로 3W간격을 유지 )

- Differential Pair는 가능한 동일한 Layer에 배치한다. (특성임피던스 매칭 때문)

- Differential Pair 양단의 길이가 맞지 않을 경우 Tuning을 해야 한다. (Coupling이 최대한 깨지지 않도록)

=======================================================================

아래는 OrCAD / Allegro PCB의 Differential Pair의 규칙을 설정하는 부분이다.

https://ansan-survivor.tistory.com/40

OrCAD PCB Differential pair CM Rule설정

https://www.parallel-systems.co.uk/pcbeditoradvanced_10netschedulingstatic/ PCBEditorAdvanced_10NetSchedulingStatic - Parallel Systems Net Scheduling: Differential Pair, Static Phase A new check for..

ansan-survivor.tistory.com

'전기전자공부 관련' 카테고리의 다른 글

| EMI/EMC 전자파 방출을 고려한 PCB설계시 중요 Tip (0) | 2019.12.26 |

|---|---|

| 고속신호 PCB설계시 리턴패스(Return Path) 고려 (2) | 2019.12.26 |

| Differential Mode Radiation(차동 모드 방사 전자파)이란? (Ground Loop Area) (0) | 2019.12.26 |

| S-parameter 란? 반사계수(VSWR, Return Loss, Γ)란? (0) | 2019.12.24 |

| LC회로 직렬연결과 병렬연결 임피던스 파형 (0) | 2019.11.29 |