임피던스를 고려한 Constraint Manager Rule설정에 대한 자세한 방법은 아래 포스팅을 참고한다.

ansan-survivor.tistory.com/490

[PCB Editor] OrCAD PCB / Allegro PCB 임피던스 자동 계산 배선, OrCAD PCB Impedance routing (라우팅)

이 기능은 Constraint Manager의 Electrical Rule과 Physical Rule 둘 다 가능하다. Physical Rule 을 이용할 땐 모든 OrCAD 라이센스에서 이용 가능하다. 그러나 Electrical Rule을 이용하면 OrCAD PCB Professio..

ansan-survivor.tistory.com

이 기능은 Allegro High Speed Option이 있어야 가능하다. (Vision Manager기능 만)

이 포스팅은 간단하게 Imedance 값에 관한 Rule을 만들고 Vision Manager를 이용해 시각적으로 쉽게 볼 수 있도록 한다.

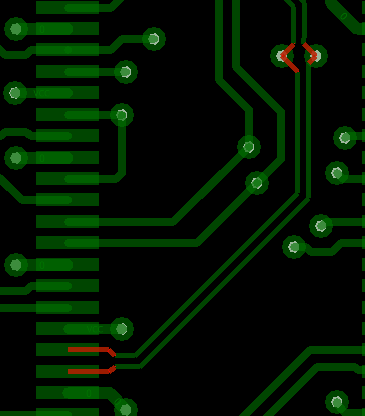

1. Constraint Manager에서 원하는 Net의 임피던스값을 설정한다. (Target Impedance를 모두 50옴으로 설정)

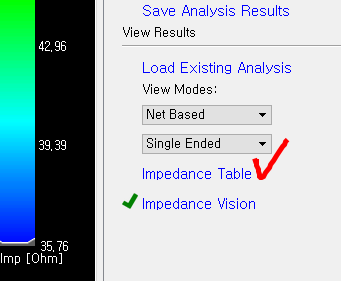

2. Analysis Mode의 Impedance활성화

3. Vision Manager 활성화

4. Vision Manager 적용

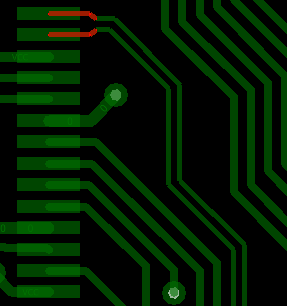

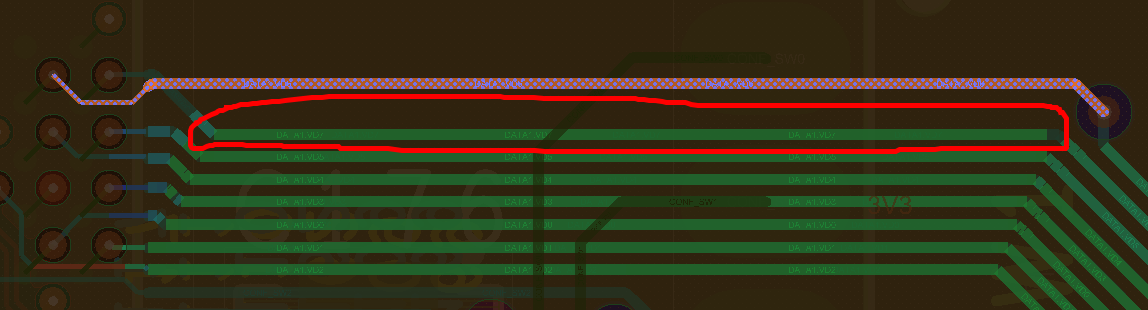

(테스트) 두께를 키워 임피던스값을 45옴으로 내리면, 해당부가 50옴 이하이므로, 파란색으로 표시된다.

(테스트) 두께를 키워 임피던스값을 50옴으로 맞추면,Rule에 적합함으로 초록색으로 표시된다.

옵션에 보면,

파란색 : Rule보다 값이 적을때

초록색 : Rule을 만족할 때

빨간색 : Rule보다 값이 클 때

<< Vision Manager로 배선 (Routing) >>

ansan-survivor.tistory.com/503

[PCB Editor] OrCAD PCB / Allegro PCB 비전매니저 사용하여 Route(배선) 하기

이 기능은 배선(Routing)시 시각적으로 도움을 주어 라우팅을 진행할 때 올바르게 되었는지 알려주는 기능을 제공한다. 또는 배선을 다 완료하고나서 어느 부분이 잘못 되었는지 시각적으로 확인

ansan-survivor.tistory.com

<< Vision Manager로 부품 배치 (Placement) >>

ansan-survivor.tistory.com/502

[PCB Editor] OrCAD PCB / Allegro PCB 비전매니저 사용하여 Placement(부품 배치) 하기

DDR을 설계시 부품을 배치하는 것도 중요하다. 사전에 잘 배치를 해야 나중에 배선할 때 여러번 수정하는 고된작업을 예방할 수 있다. OrCAD PCB에서는 Rule을 미리 주고, 배치할 때 해당 범위내에 들

ansan-survivor.tistory.com

<< Vision Manager로 리턴패스 Rule 시각화 (Return Path Rule) >>

ansan-survivor.tistory.com/208

[PCB Editor] Allegro PCB Designer, High speed option 비전매니저로 Return Path DRC 찾아내기

아래 작업은 이전포스팅의 Return Path를 바탕으로 만들어서 Vision Manager를 적용해보았다. https://ansan-survivor.tistory.com/207 [PCB Editor] Allegro PCB Editor High speed Option, Return path Constrai..

ansan-survivor.tistory.com

<< Vision Manager로 IR Drop 시뮬레이션 시각적 분석 >>

https://ansan-survivor.tistory.com/1032

[PCB Editor] <Vision Manager> OrCAD / Allegro PCB 비전매니저 IR Drop 시뮬레이션 시각적 분석

이 옵션을 사용하기 위해서는 아래와 같은 조건이 만족해야 한다. 1. Allegro PCB Designer High Speed 옵션 또는 Allegro Venture 라이센스 필요 2. Sigrity Clarity 가 설치되어 있고 라이센스를 보유해야 함 I..

ansan-survivor.tistory.com