이 기능은 Constraint Manager의 Electrical Rule과 Physical Rule 둘 다 가능하다.

Physical Rule 을 이용할 땐 모든 OrCAD 라이센스에서 이용 가능하다.

그러나 Electrical Rule을 이용하면 OrCAD PCB Professional 이상의 버전에서 가능하다.

고속의 PCB를 설계할 때 Sinal Integrity (신호의 무결성)으로 인해 임피던스 매칭이 필요하다. 그 임피던스값을 조절할 수 있는 요소가 여러가지가 있는데 아래와 같다.

ansan-survivor.tistory.com/489

PCB 배선시 전송선로 임피던스 매칭 값 쉽게 도와주는 사이트, impedance 값 계산 웹

고속신호의 PCB를 설계할 때 신호의 무결성을 위해 여러 요소값들을 계산해주어야 하는데, 대표적으로 많이 사용하는 Microstrip 타입의 전송선로 계산식은 아래와 같다. 그러나 이를 손으로 엑셀

ansan-survivor.tistory.com

하지만 OrCAD PCB에서는 이 계산을 알아서 해주므로 직접 계산할 필요가 없다.

임피던스에 영향을 줄 수 있는 4가지 요소중, 대부분 Trace의 Width를 변경하여 임피던스를 맞춤으로 OrCAD PCB에서도 나머지 값을 다 입력하고, 원하는 임피던스값을 넣으면 알아서 Width가 맞춰진다.

임피던스 계산 기능을사용하기 전에 Stack up에서 Cross section에 관한 속성값을 먼저 넣어햐 한다.

stack up layer 방법은 아래 블로거님께서 잘 정리해 주셨다.

OrCAD 17.2 사용법) Layer(Cross-Section) 설정하기

(이 글은 17년 11월 3일에 수정하였습니다.)(16.6 이하 버전은 http://blog.naver.com/kingreddrake/220637...

blog.naver.com

또한 예전에 Flexible PCB stack up 관련 정리해놓은 자료가 있다.

ansan-survivor.tistory.com/587

[PCB Editor] OrCAD PCB / Allegro PCB Cross-Section Layer(단면 레이어)의 생성 순서 및 Layer 순서 변경하기, 필

PCB의 단면도인 Cross-section을 만드는 방법은 아래와 같다. 1. Pair Layer 추가하기 아무 Layer를 잡고 마우스우클릭을 하면 아래와 같은 팝업창이 뜨는데, "Add Layer Pair Above/Below" 하면 Conductor(도선)..

ansan-survivor.tistory.com

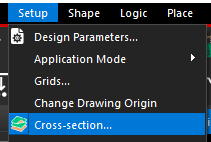

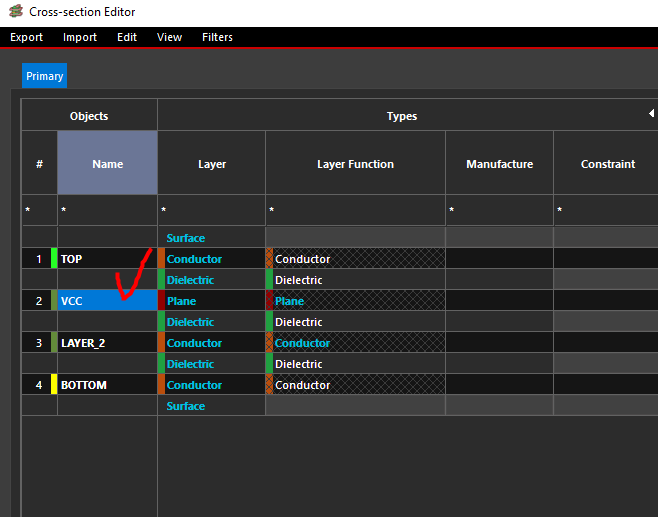

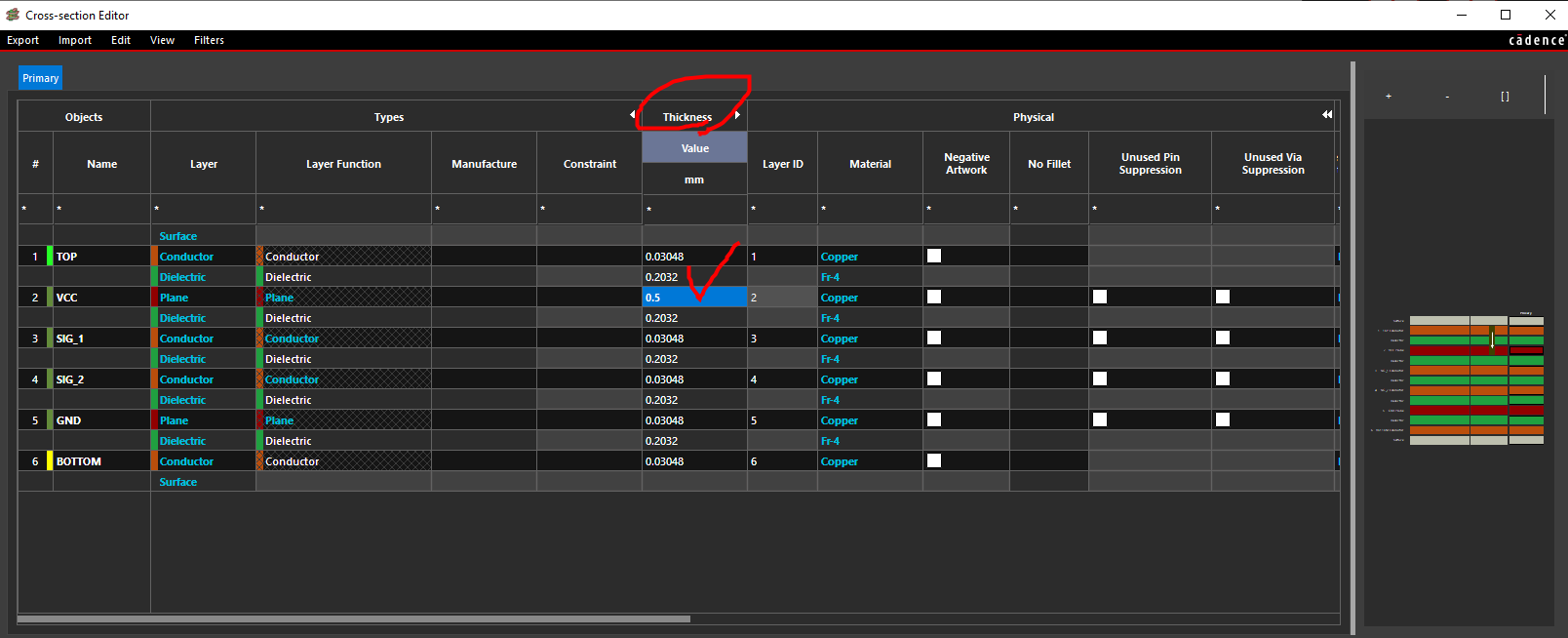

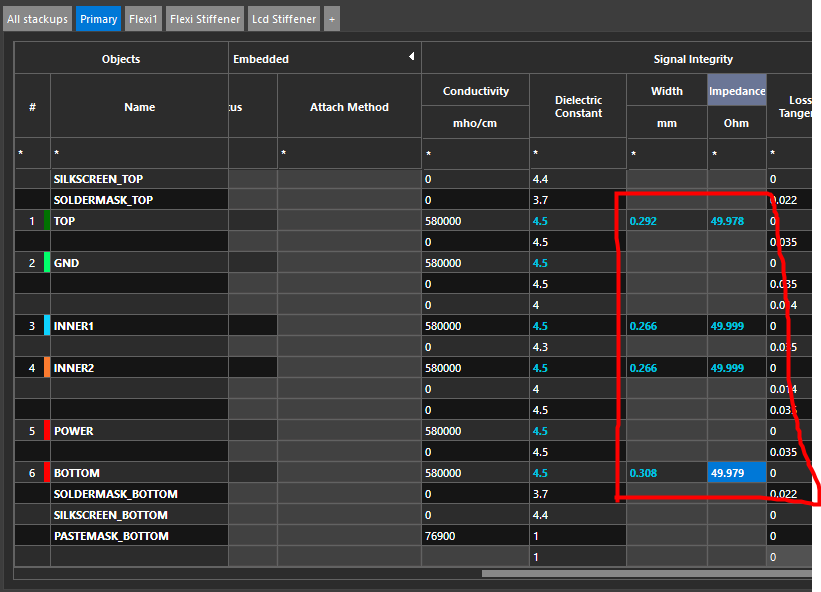

Setup - Cross-section 에 들어가면 아래와 같이 단면도(Cross-section)정보를 볼 수 있다.

Primary (main pcb layer만 보기)

conductor (배선 layer), Dielectric (유전체) , Plane (copper 판)

Thickness (각 layer의 두께), Material (재료 성분)

Dielectric Constant (유전율)

Impedance (임피던스값)

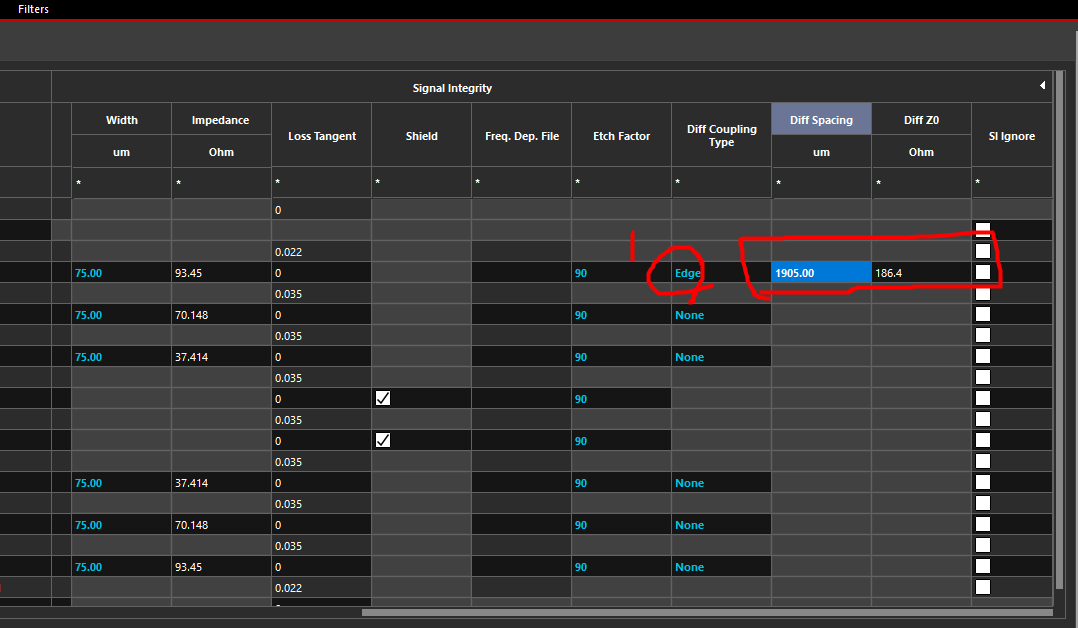

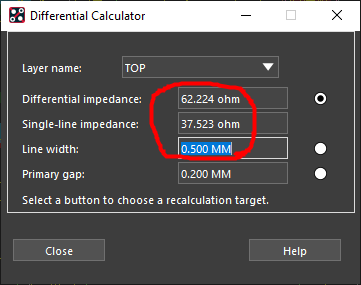

* Differential Pair 관련한 임피던스 자동 계산하는 방법은

Cross-Section의 Signal Integrity에 Diff Coupling Type 을 Edge로 두고, Diff Spacing과 Diff Z0 값을 보면 된다.

(Diff spacing : diff pair간 간격 / Diff Z0 : 타켓 임피던스값)

==============

<Physical Rule으로 임피던스 값 계산 방법>

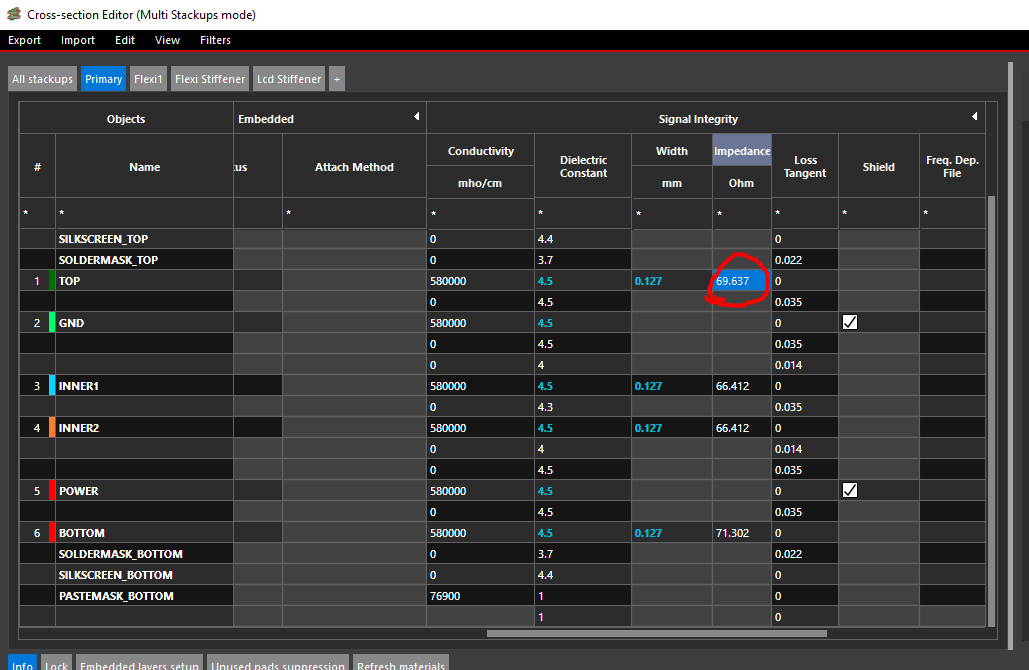

1. 임피던스값 변경으로 Trace의 Width를 얼만큼 해야 하는지 확인

Cross-section에서 Signal Integrity의 Impence값을 원하는 임피던스값으로 변경하면, 자동으로 Width값이 바뀐다.

여기서 유의해야할점이, Width가 바뀌었다고 내가 배선할 때 저 값으로 배선되는게 아니라, 참고할 수 있는 값이다.

배선 두께를 강제화 하는것은 Constraint Rule에서 하는 것이고, 여기서는 어떤 값을 배선에 넣을지 참고하는 것이다.

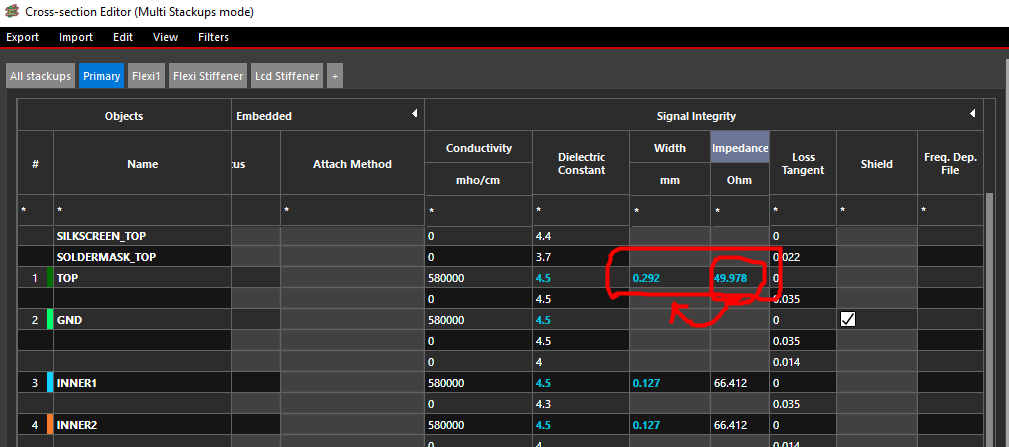

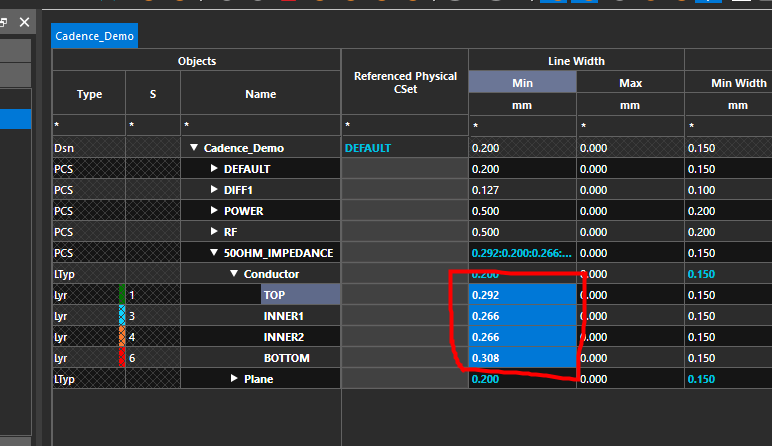

이제 50옴 임피던스를 맞추기 위해서는 0.292mm width로 배선해야 됨을 확인했다.

50옴 임피던스를 위해서는...

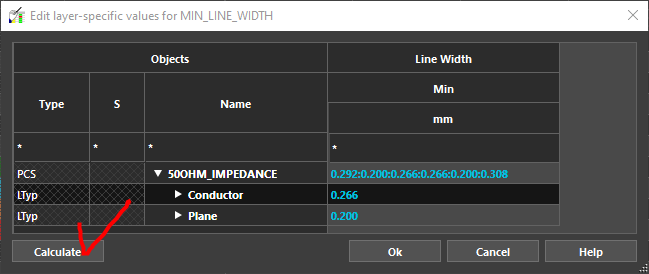

Top: 0.292, Bottom: 0.308, Inner1: 0.266, Inner2: 0.266 으로 배선해야 한다.

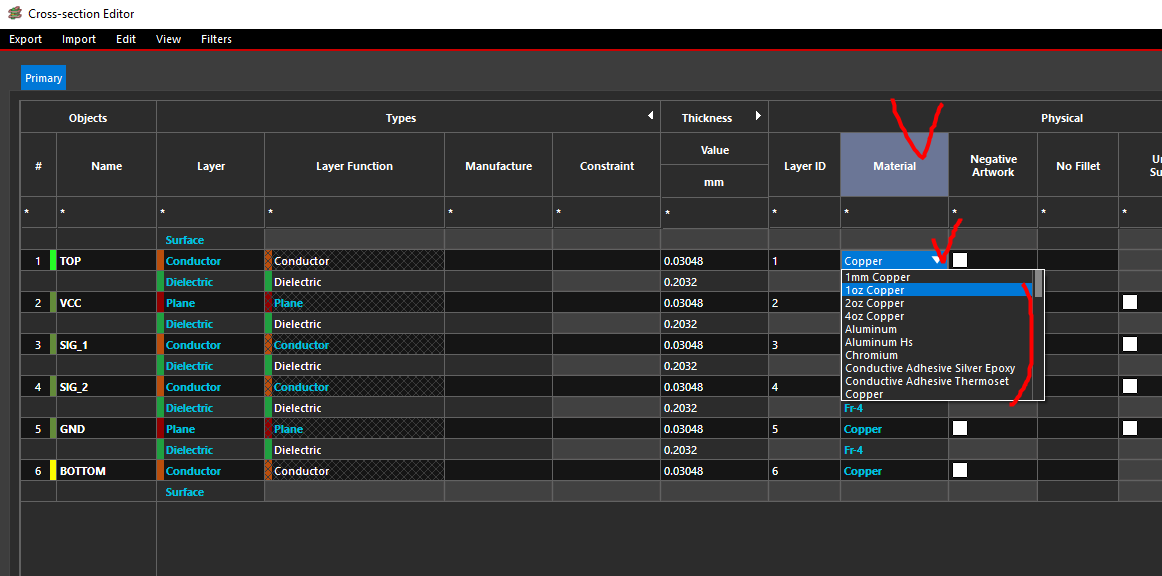

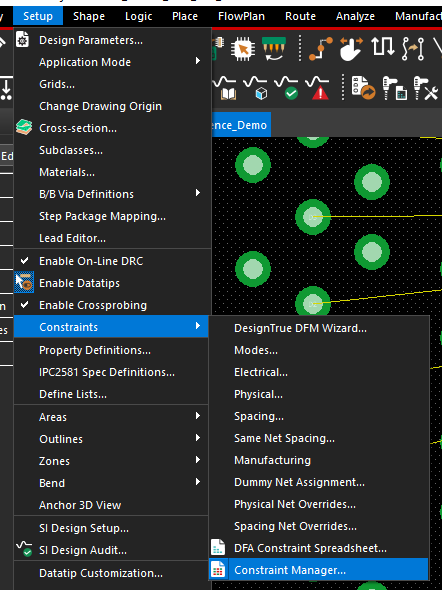

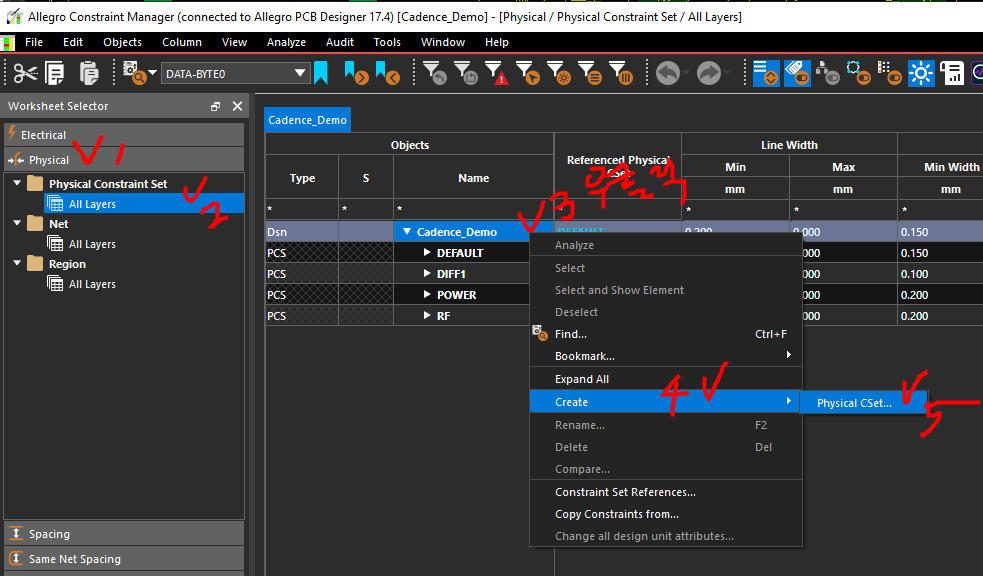

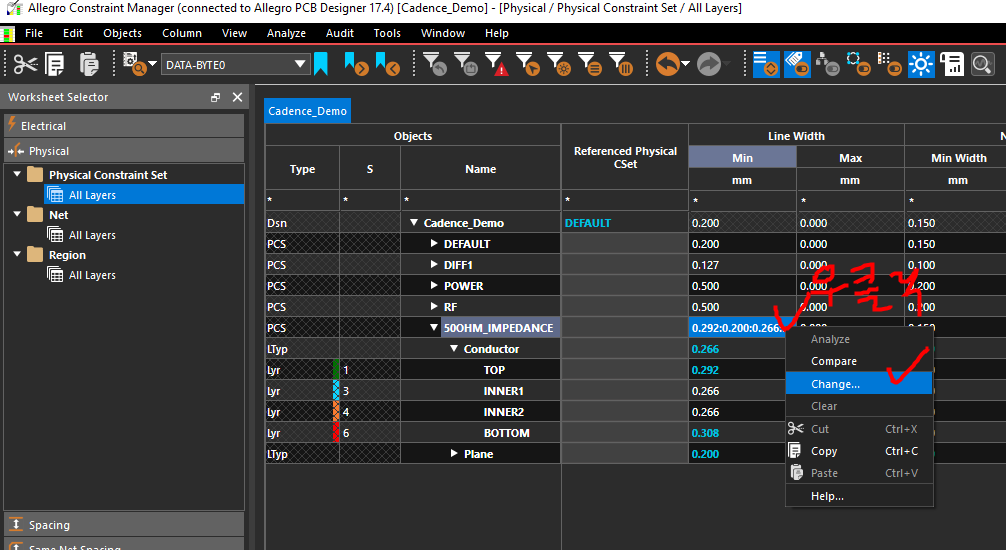

2. Constraint Manager로 Trace Width 배선 Rule지정

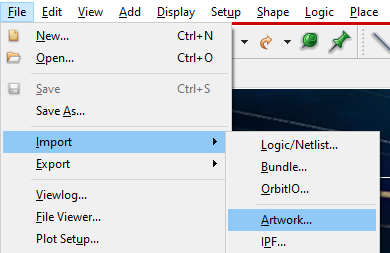

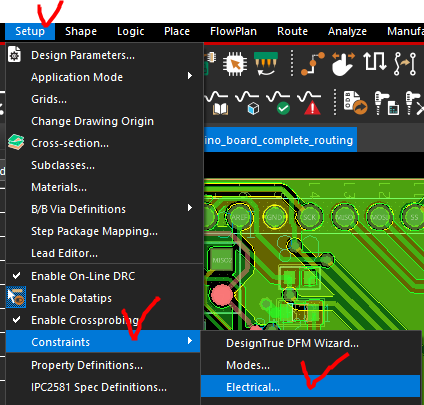

2-1. setup - Constraints - Constraint Manager

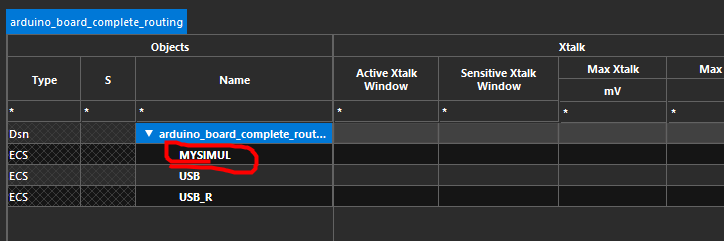

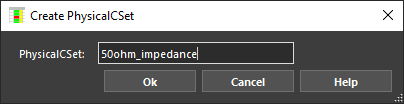

2-2. 새로운 Class Set을 만듦

3. 언더바를 눌러 확장시킨 후, 해당 Layer별 Line Width값 확인, 아까 확인한 값을 입력

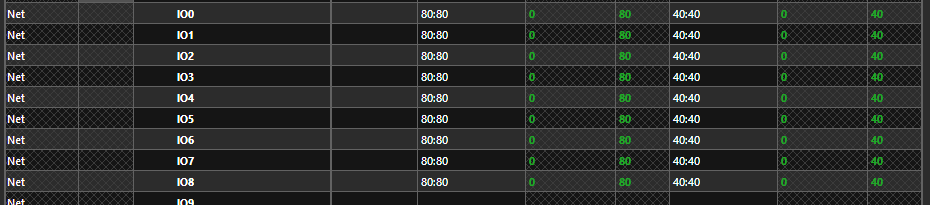

4. Set값을 적용하기 위해서는 Net에서 Class를 지정

(결과)

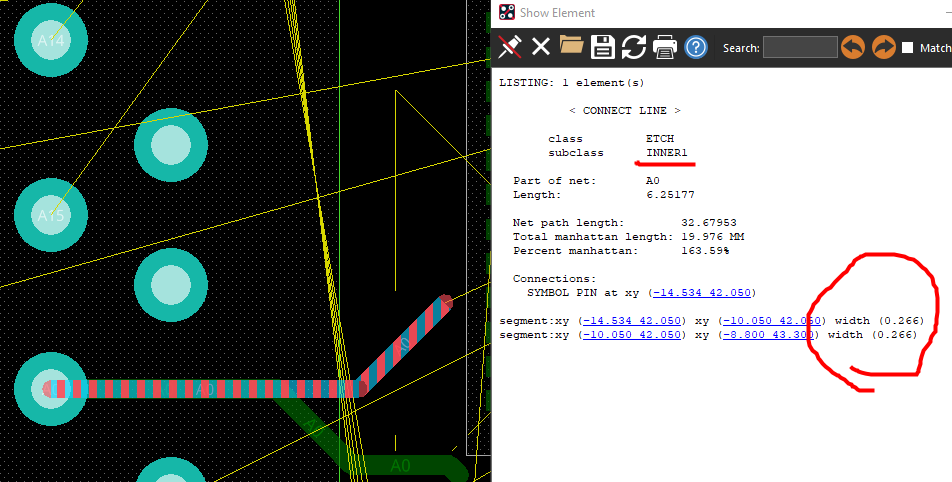

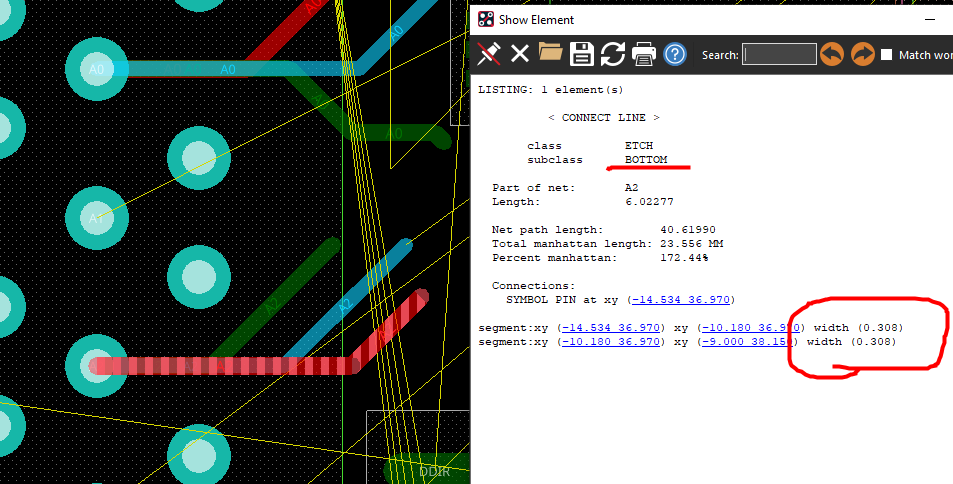

Top layer에서 배선할 때 0.292로 width가 잡힌다.

INNER1 에서는 0.266 으로 잡힌다.

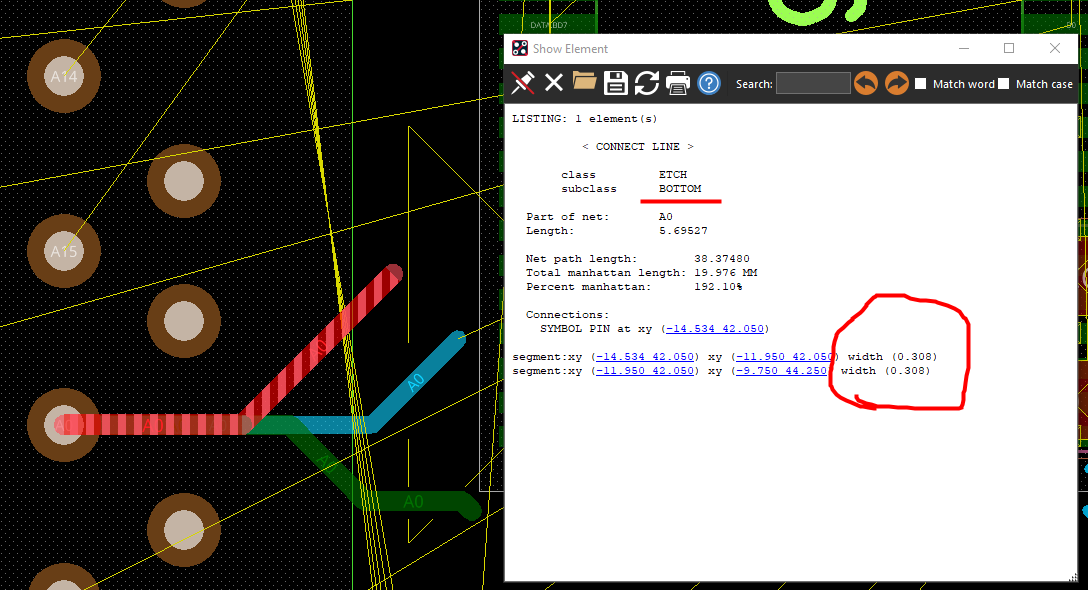

Bottom에서는 0.308으로 잡힌다.

==============

(OrCAD PCB Professional 이상의 버전에서 가능하다.)

<Electrical Rule으로 임피던스 자동 계산 및 배선두께 강제화 방법>

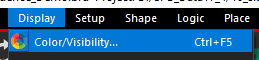

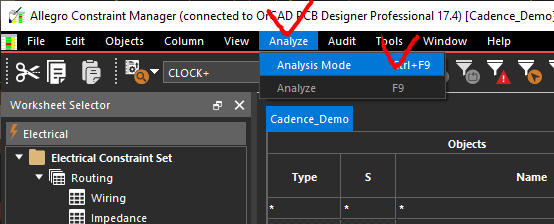

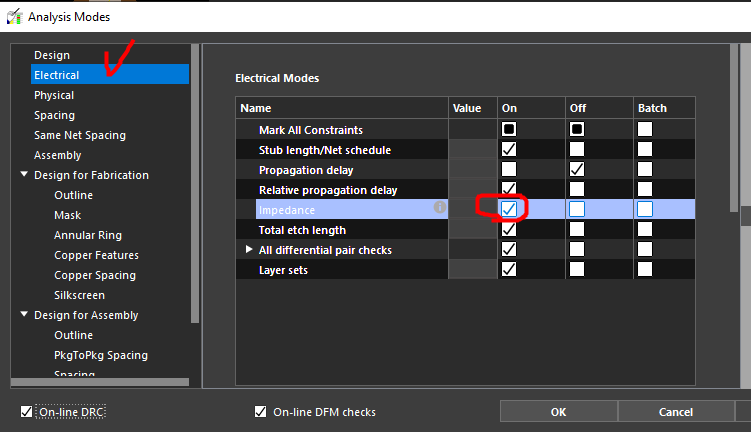

0. Analyze 모드 활성화

Analyze - Analysis Mode

Electrical - Impedance - On 체크박스 활성화

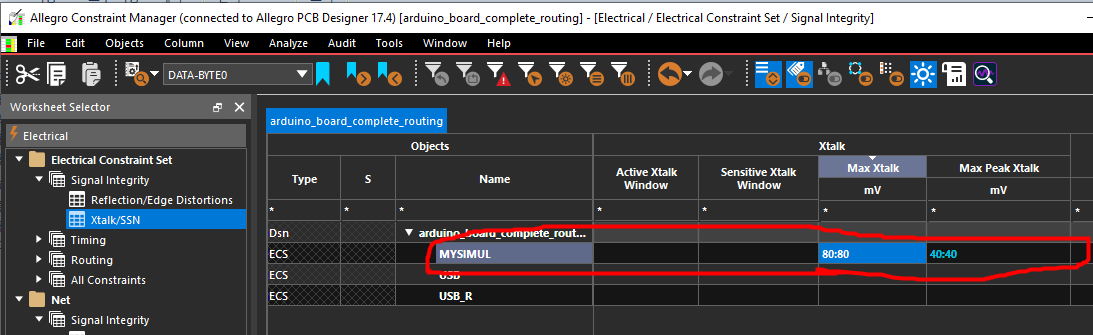

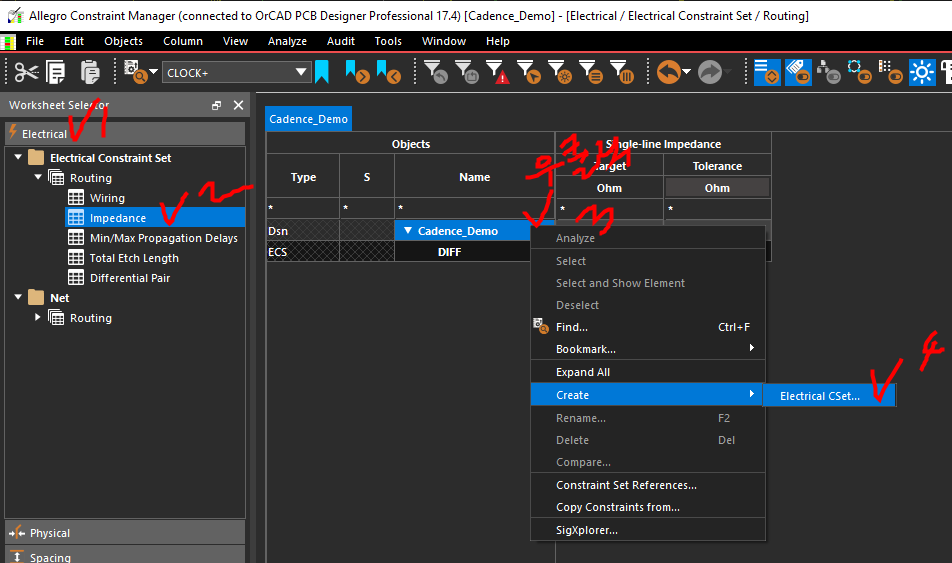

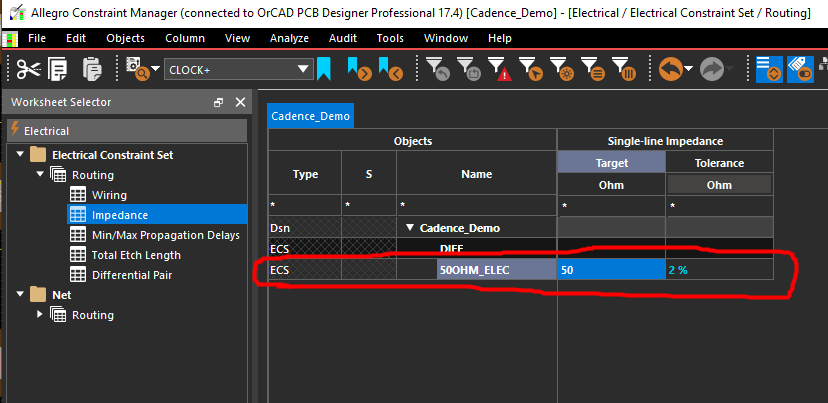

1. Electrical - Impedance - 우클릭 - Create - Electrical CSet

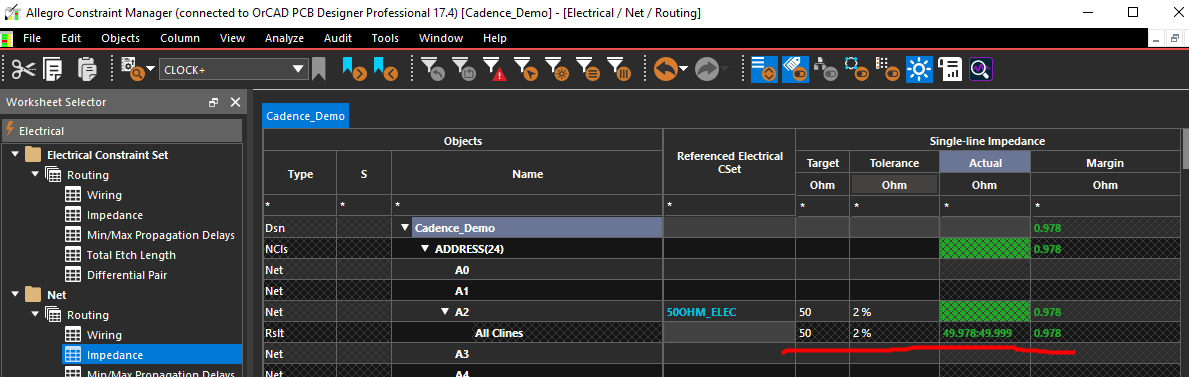

"50ohm_elec"이라는 class를 만들고, Target값에 50옴 입력

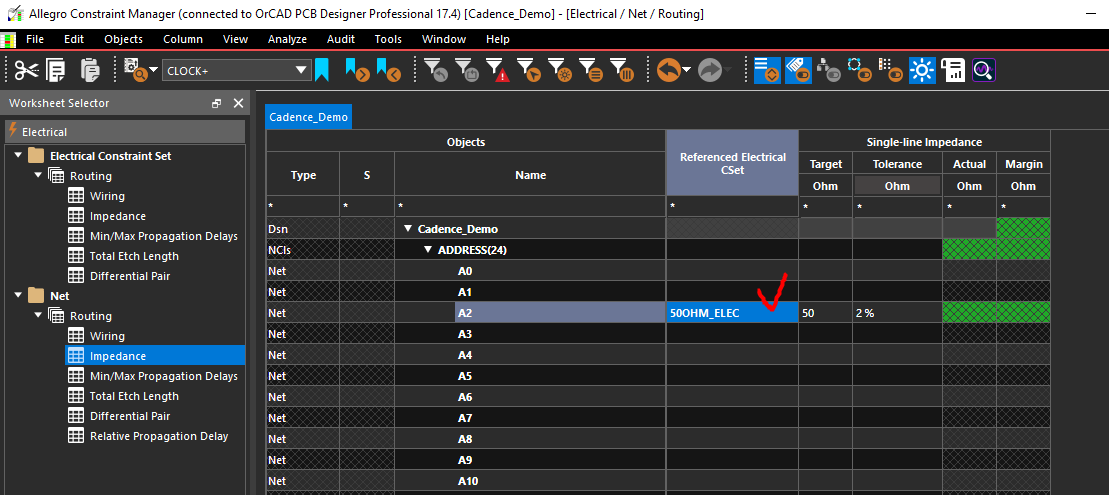

2. Net에 룰 적용

그러면 50옴에 맞도록 width가 알아서 조절된다.

(결과) 마찬가지로 layer별로 임피던스값이 50옴이 되도록 알아서 width가 고정된다.

Electrical 룰을 사용하면 위처럼 Cross-section에서 값을 찾고 Physical룰에서 값을 적용하는 이런 번거로움을 덜 수 있다.

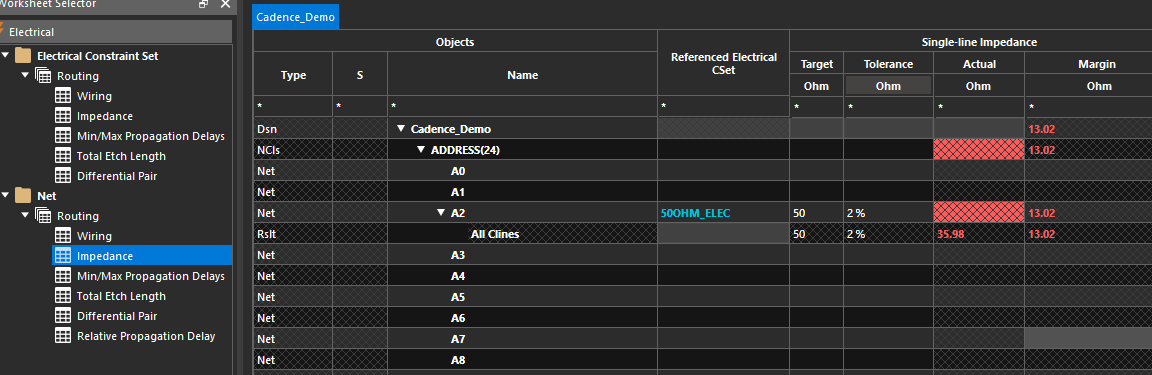

Constraint Manager에서 Target값, Actual값, Margin값이 만족하는지 실시간으로 볼 수 있다.

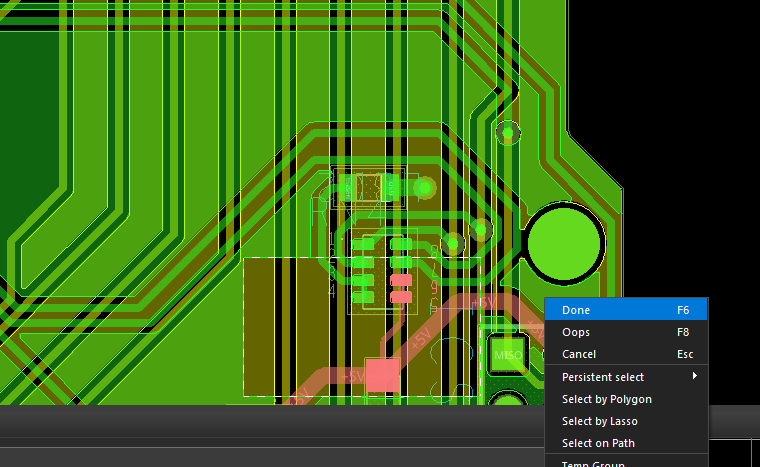

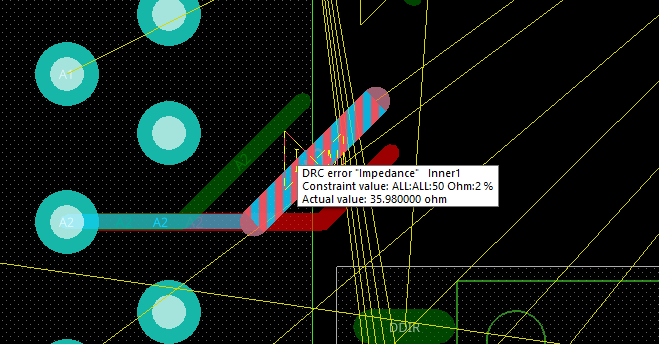

(테스트) 일부러 두께를 늘려서 임피던스 값을 낮춰봤다. 그러면 DRC마커와 함께 위반한 내용이 뜬다.

50옴의 마진이 +-2%를 벗어남으로 아래와 같이 Constraint Manager에서 DRC가 뜬다.

이렇게 Electrical Rule을 이용하면 손쉽게 어떤 Trace의 50옴 임피던스를 쉽게 설계할 수 있다.

아래 영상을 참고하여 만들었다.

www.youtube.com/watch?v=PTFfJyQUr74

(참고)

Physical Rule과 Electical Rule 둘다 적용했을 때, Electrical Rule이 더 우선순위를 차지한다.

Allegro PCB Designer이상의 라이센스에서는 Trace의 임피던스값을 볼 수 있는 옵션을 제공한다.

실제로 기생성분들 RLC값을 모두 볼 수 있다. (아래 링크 참고)

ansan-survivor.tistory.com/464

[PCB Editor] Allegro PCB 기생성분 RLC 보기, 전송선로(Trace)나 동박(Plane)에 임피던스, 저항, 캐패시턴스

이 기능은 Allegro PCB Designer 이상 라이센스에서만 지원한다. 고속PCB설계를 할때, 임피던스 매칭이 중요하다. 그리고 그외 얼마나 많은 기생성분들 RLC가 있는지 궁금할 때, Allegro PCB Designer에서는

ansan-survivor.tistory.com

<Tip>

임피던스값과 Trace Width값을 임시로 계산하고 싶을 때

각 Net 배선의 임피던스가 어떻게 되는지 시각적으로 보여주는 기능

https://ansan-survivor.tistory.com/504

[PCB Editor] <Vision Manager> OrCAD PCB / Allegro PCB 비전매니저 사용하여 Impedance (임피던스) DRC 시각적으로

임피던스를 고려한 Constraint Manager Rule설정에 대한 자세한 방법은 아래 포스팅을 참고한다. ansan-survivor.tistory.com/490 [PCB Editor] OrCAD PCB / Allegro PCB 임피던스 자동 계산 배선, OrCAD PCB Impe..

ansan-survivor.tistory.com