아래 Net만의 Topology가 보고 싶을 때,

1. Constraint Manager 실행

2. 보고자하는 Net를 찾는다.

Electrical - Net - Wiring - 원하는 네트 선택

3. Sigxplorer 실행

Tools - SigXplorer

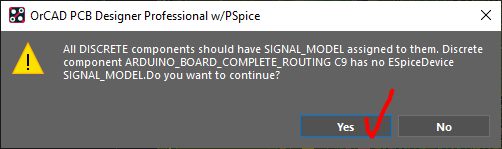

(결과) 해당 토폴로지가 보여진다. 그러나 Driver, VCC, GND, Receiver 등 설정이 없으므로 SI 시뮬레이션은 안된다.

아래 Net만의 Topology가 보고 싶을 때,

1. Constraint Manager 실행

2. 보고자하는 Net를 찾는다.

Electrical - Net - Wiring - 원하는 네트 선택

3. Sigxplorer 실행

Tools - SigXplorer

(결과) 해당 토폴로지가 보여진다. 그러나 Driver, VCC, GND, Receiver 등 설정이 없으므로 SI 시뮬레이션은 안된다.

이 기능은 Allegro PCB Designer이상의 옵션이 있어야 사용가능하다. (OrCAD Professional 라이센스로 사용 불가)

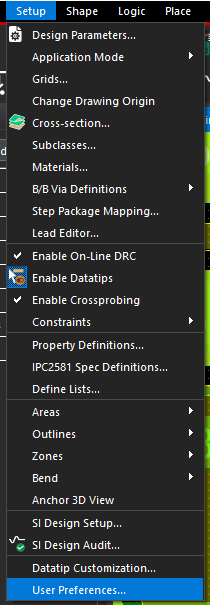

회로 설계에 대한 도면이 없고, Netlist도 없을 때 PCB상에서 Net를 수정할 필요가 있을 때, 아래와 같이 Net를 변경할 수 있다.

이 테스트에서 D- 네트와 RD- 네트를 하나로 통합하여 D- 라는 이름으로 모두 바꿔줄 것이다.

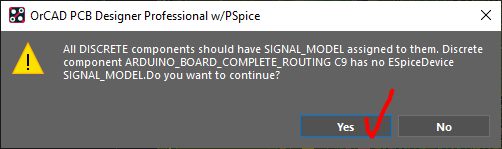

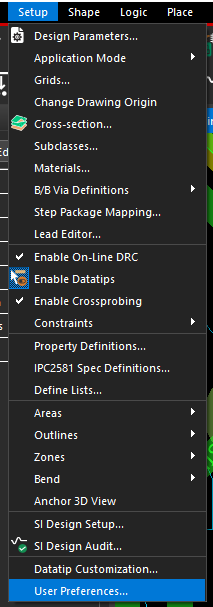

1. PCB상에서 임의로 Net를 변경하려고 할때 아래와 같이 Preference를 변경해야 한다.

Logic - logic_edit_enabled 활성화

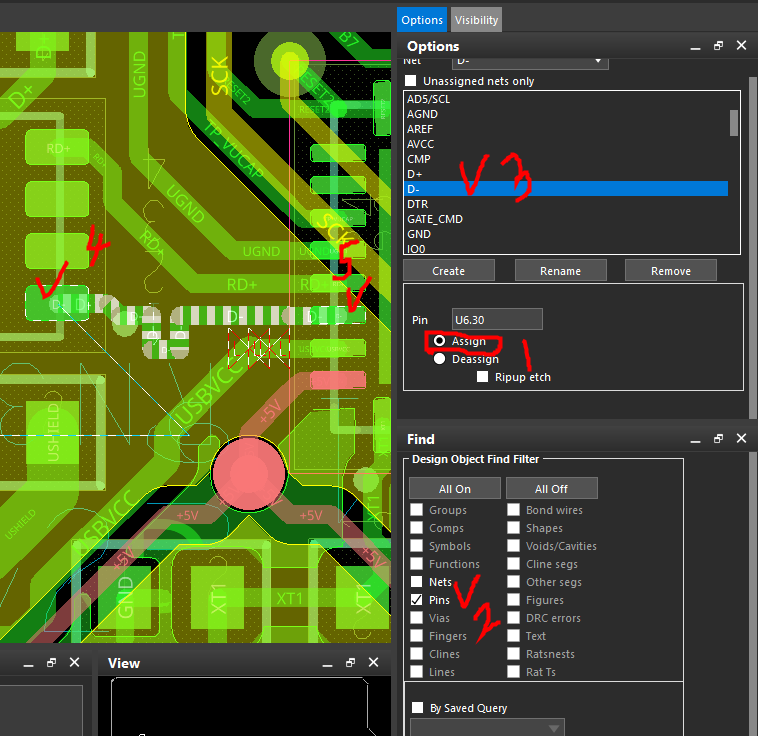

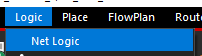

2. Logic - Net logic

그러면 우측 Options창이 아래와 같이 활성화가 된다.

3. Net 제거 및 할당

RD- 네트를 찾아서 제거한다. (여기에는 현재 PCB상에 있는 모든 Net가 표시된다.)

4. 원하는 Net를 할당한다. 여기서 D- 네트를 할당할 것이다.

Net를 할당하기 위해서는 Dummy Pin으로 변한 아래 핀들에게 D- 네트를 할당해야 한다.

그러면 자동으로 연결된 cline도 D-으로 할당이 된다.

(결과) 모두 D-라는 Net로 바뀌었다.

아래는 OrCAD Capture의 회로도 없이 Net를 PCB상에서 생성하는 것

ansan-survivor.tistory.com/455

[PCB Editor] OrCAD PCB / Allegro PCB OrCAD Capture 회로도 없이 네트 만들기

보통 PCB에서 Net는 OrCAD Capture에서 Netlist로 넘겨 생성되는 Netlist로 PCB설계를 진행한다. 그러나 그냥 PCB Editor를 열면 Netlist가 없기 때문에, Net정보 또한 없다. 아래 처럼 원하는 net를 만들 수 있다..

ansan-survivor.tistory.com

Net의 스케줄 관리는 아래 링크 참고

https://ansan-survivor.tistory.com/209

[PCB Editor] OrCAD / Allegro PCB Designer, Net Schedule 사용하기, 네트 스케쥴링

OrCAD Professional 이상의 라이센스가 필요하다 (Allegro PCB Designer 라이센스는 기본적으로 포함) 어떤 Topology를 원하는 방법으로 생성하거나, 수정할 때 이용하면 좋을 것이다. Allegro 라이센스를 활성

ansan-survivor.tistory.com

OrCAD Capture에서 회로도를 그릴때 미리 특성값을 넣어서 신호의 무결성 시뮬레이션을 할 수 있다.

PCB를 제작하기전에 Logic회로에서 어떤 특성값에따라 신호가 어떻게 나오는지 미리 확인할 수 있다.

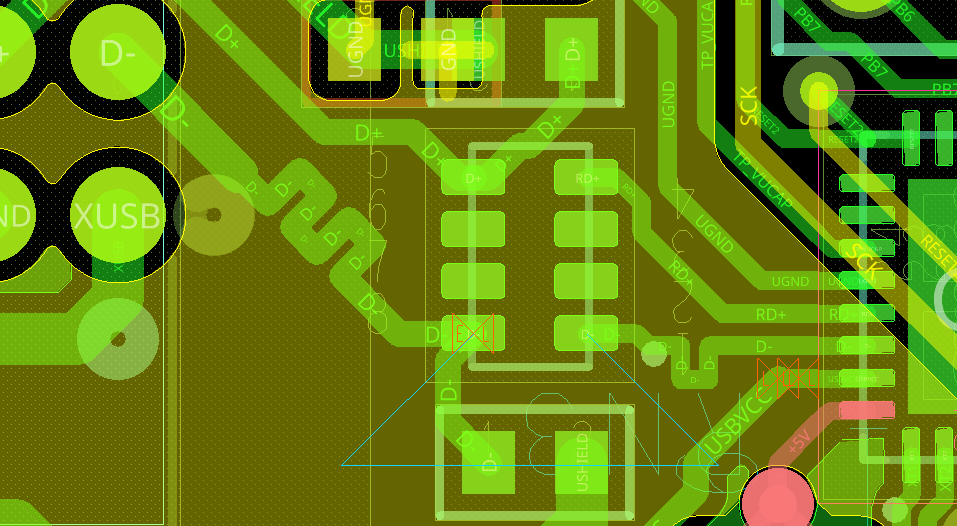

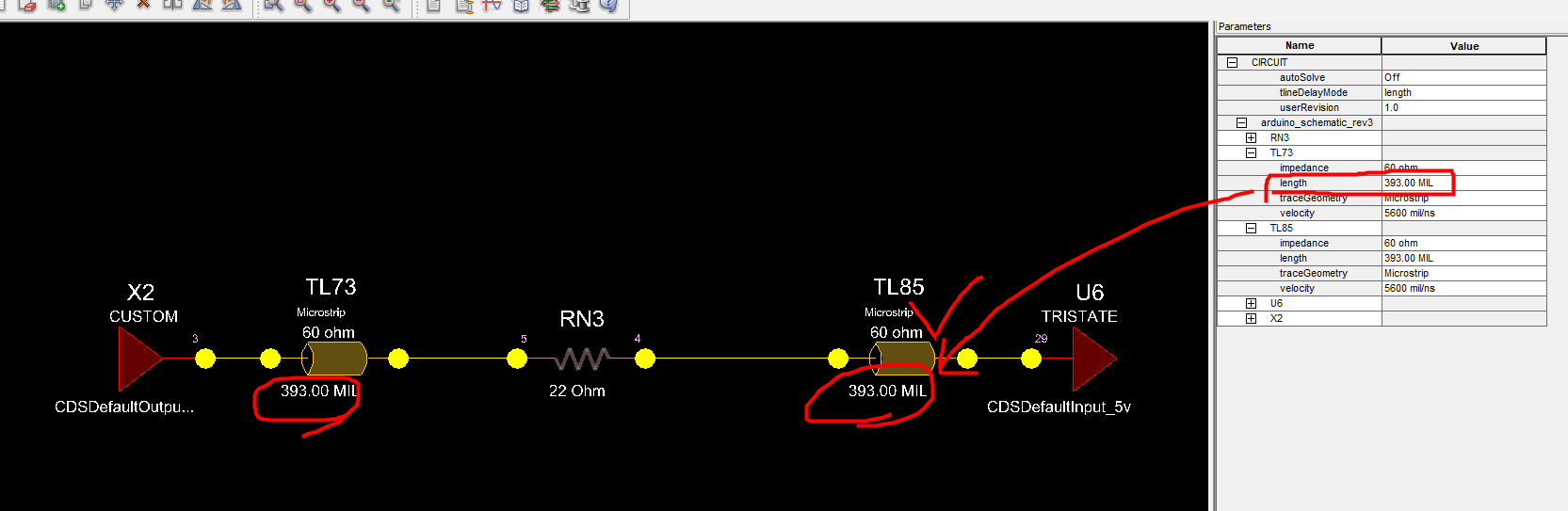

아래와 같이 USB D+ 신호가 IC의 D+ receiver로 잘 들어가는지 시뮬레이션을 할 것이다.

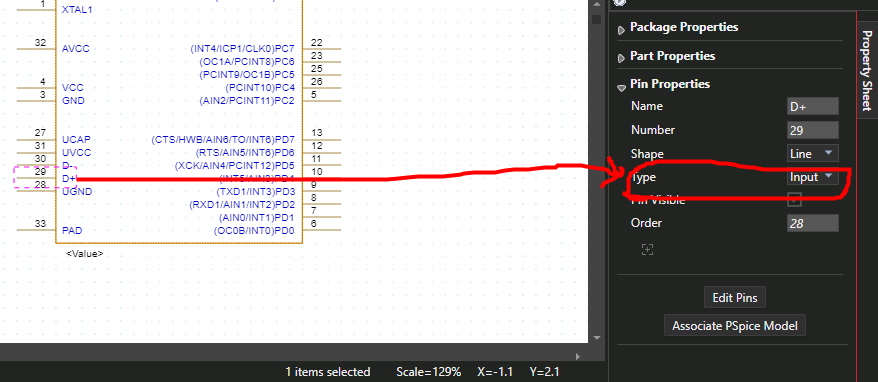

그러기 위해서 우선 모두 Part Edit를 통해 passive로 되어있는 핀 type을 output, input으로 바꿔준다.

1. 핀에 SI 모델 부여

Sender핀만 클릭 - 마우스우클릭 - SI Analysis - Assign SI Model

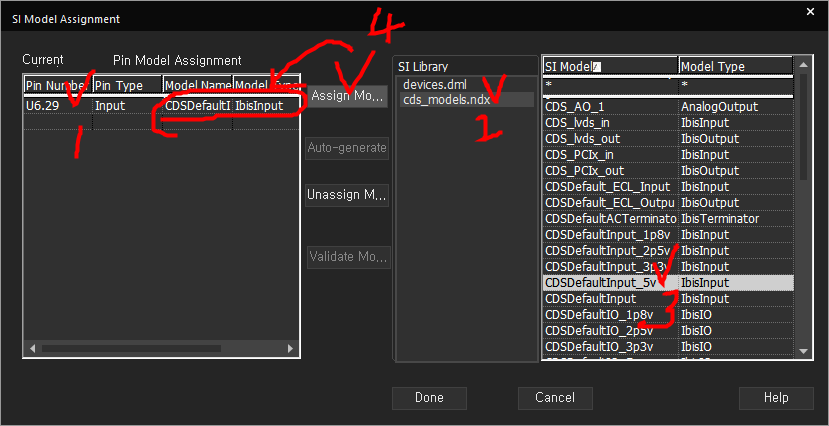

2. 아래와 같은 순으로 X2의 3번핀에 SI Model을 부여

(Cadence에서 제공하는 5V짜리 output 모델을 부여했다)

3. 전송선상에 있는 저항에도 SI모델을 부여해준다.

마우스우클릭 - SI Analysis - Assign SI Model

4. 마지막 Receiver에게도 SI Model을 넣어준다.

마우스우클릭 - SI Analysis - Assign SI Model

아래와 같은 순으로 U6의 29번핀에 Input 관련 SI Model을 부여

5. 해당 Net에서 Explore Signal 프로그램을 연동시켜 실행시킨다.

(17.4버전의 버그인지는 모르겠지만, Topology가 해당 Pin pair만 나온게 아니고 전부다 나왔다;;)

내가 설정한 부분은 여기에 있다.

이 부분을 빼고 나머지를 다 지웠다..

6. 보고자 하는 관점을 선택할 수 있다.

여기에서는 PCB의 관점으로 보기위해 time대신, Length(길이)로 택했다.

7. 이름부분을 클릭하면, 아래와 같이 Stimulus Edit 창이 뜬다.

8. Custom으로 변경 후 보내고자 하는 신호를 정한다.

원하는 주파수와 테스트 패턴을 정하면 아래와 같이 그래픽적으로 수정된다.

9. 시뮬레이션 시작 버튼

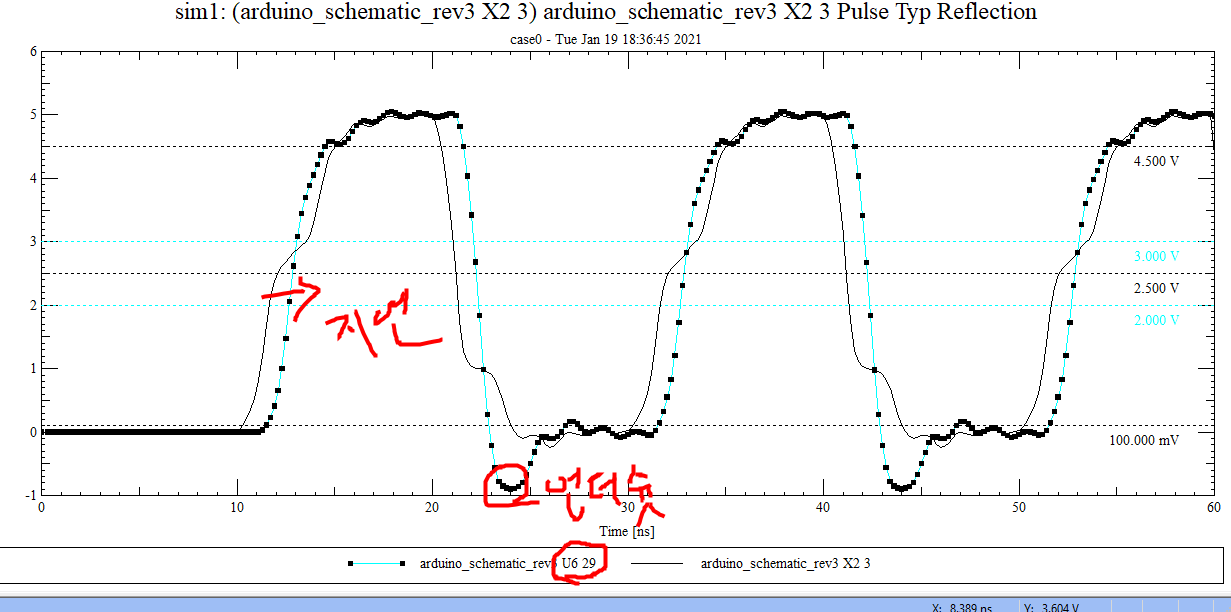

10. 시뮬레이션 결과

X2의 3번핀, 즉 Sender에서 보낸 파형

U6의 29번핀, 즉 Receiver에서 받은 파형 (delay와 undershoot 까지 있다)

11. 길이를 짧게 수정하고 다시 시뮬레이션을 해보았다.

수정 방법은 그냥 클릭하고 length 의 숫자만 변경시켜주면 된다.

시뮬레이션 결과, 전송선로를 짧게 만들었더니 (당연히) Sender에서 보낸 신호가 Receiver에게 잘 전달 되었다.

이 기능을 이용해서, PCB를 설계하기전에 회로설계에서 전송선로의 Length를 얼마큼 할지 잘 고려해보면 좋을 것 같다.

<TIP>

SigXplor 는 기본적으로 mil단위로 세팅 되어있는데, 이를 mm를 기본으로 바꾸기 위해서는 env파일을 수정해야 한다.

ansan-survivor.tistory.com/216

[PCB Editor] OrCAD / Allegro PCB Editor 환경설정(user preference) / 단축키 만들기.

Allegro PCB Editor에는 ENV파일이 있다. 이 파일은 유저가 사용하는 작업환경 정보를 담고 있다. 이 ENV파일은 3종류로 나눠질 수 있는데, Global ENV파일 : 설치시 자동으로 생기는 Default 환경설정 파일 SI

ansan-survivor.tistory.com

env 환경설정 하는 방법은 위 링크 참고 바란다. 그리고 env파일을 열고 아래 한줄만 추가하면 된다.

여기서 mm단위를 기본으로하고, 숫자 2는 소수점 자리수 이다.

set SIGXP_ALTERNATE_UNITS "millimeters 2"

다음 영상을 참고했다.

www.youtube.com/watch?v=7_iQouiLFlc

resources.orcad.com/high-speed-design/have-orcad-capture-you-also-have-signal-integrity-capabilities

Have OrCAD Capture? You also have Signal Integrity Capabilities

The inherent need to address signal quality challenges is no longer limited to just high-end, high-speed, signal integrity experts. OrCAD provides an integrated analysis environment with powerful...

resources.orcad.com

이 기능은 Allegro PCB Designer 이상 라이센스에서만 지원한다.

고속PCB설계를 할때, 임피던스 매칭이 중요하다. 그리고 그외 얼마나 많은 기생성분들 RLC가 있는지 궁금할 때, Allegro PCB Designer에서는 쉽게 볼 수 있도록 자동으로 계산해서 보여준다.

1. Display - Parastic

2. Find에서 어떤것을 볼지 선택

3. Cline을 클릭하여 확인

클릭하면, 아래와 같이 Text로 기생성분들의 값이 계산되어 나온다.

(Trace의 두께를 늘려서 임피던스 감소시켜보기)

4. 동박의 기생성분 보기

*단, Parastics Report는 Ideal Plane이라는 가정의 값이다. 반면, 아래링크의 Workflow Impedance는 Sigrity(시뮬레이션 툴)기반 Fielder Solver를 사용하고, Ideal하지 않는 plane을 사용한다.

ansan-survivor.tistory.com/496

[PCB Editor] OrCAD PCB / Allegro PCB Workflow Manager로 Impedance 보기

이 옵션은 17.2버전 이상의 OrCAD Professional, Allegro PCB 이상의 라이센스에서 사용가능하다. 1. Analye - Workflow Manager 그러면 이러한 옵션창이 새로 추가된다. Floting 하게 쓸 수 있고, 아니면 Dockin..

ansan-survivor.tistory.com

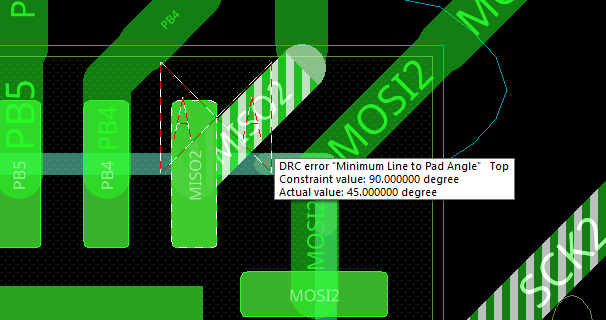

설계가 끝나고 실제로 제조(Manaufacturing)에 들어갈 때, Pad와 배선의 각이 중요하다.

Allegro PCB에서 배선할 때, Pad에 들어가거나 배선에서 배선이 뻗어나오거나 Shape과 배선이 들어가는 각도 등 원치않는 배선을 피하기 위해 Rule을 지정해 줄 수있다.

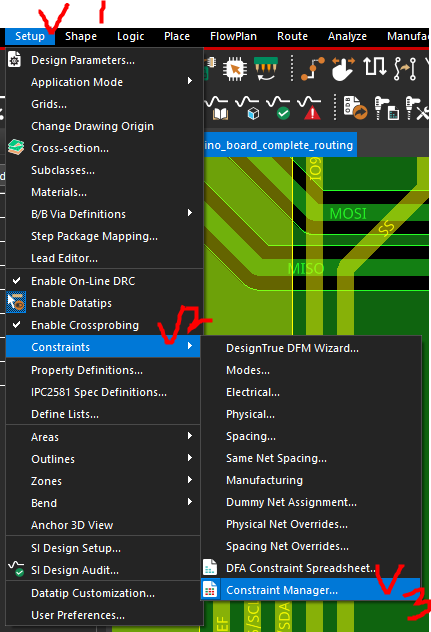

1. 아래와 같이 Constraint Manager(CMRule)를 연다.

2. Constraint Manager에서 Analyze - Analysis Mode

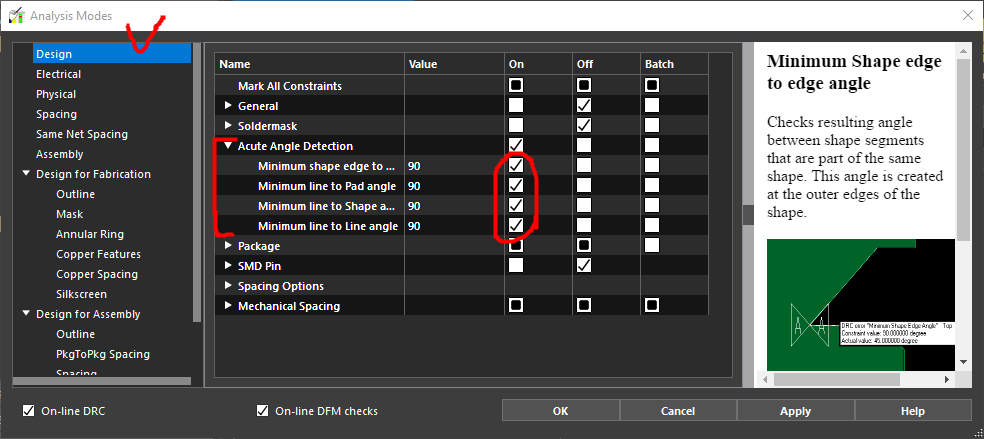

3. Anaylsis Mode 창에서 Design탭 - Acute Angle Detection

그리고 On으로 활성화를 시켜준다. (기본적으로 Electrical Rule은 비활성화 되어있음으로 활성화 시켜줘야 한다)

룰이 의미하는것은 오른쪽에 친절하게 설명이 나온다.

최소의 Shape의 꺾인각 (임피던스, 노이즈 영향)

Pad에 진입하는 최소의 배선각 (DFM제조적 관점, 임피던스 매칭 관점)

Shape에 진입하는 최소 배선각

배선시 최소의 꺾인각 (90도 이상 꺾이는 경우 곡선으로 변경, 그 이하 45도 각으로 배선)

4. 그리고 나서 DRC체크를 돌려본다.

(결과) 룰에 벗어난 부분에 DRC마커가 생겼음으로 수정해준다.

발생한 DRC의 배선각을 수정하여 사전에 설계 실수를 방지 할 수 있다.

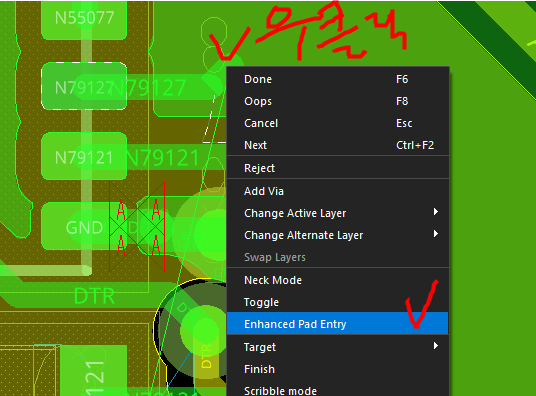

(TIP) 배선시 저런 실수를 방지하기 위해 Allegro PCB에서는 아래와 같은 기능을 제공한다.

배선중, 마우스우클릭 - Enhanced Pad Entry를 하면, 대체적으로 직각으로 Pad에서 뻗어 나오도록 도와준다.

기본 세팅으로는 Enhanced Pad Entry가 설정되어있는데, 이를 비활성화 시키려면 아래와 같이 한다.

아래 영상을 참고했다.

www.youtube.com/watch?v=vX7HKLKGhoA

이 CMRule을 사용하기 위해서는 라이센스 Allegro PCB Designer의 High-speed option이 있어야 한다.

어떠한 한 네트를 기준으로 다른 네트의 길이를 조정하고 싶을 때, Formula를 이용하면 쉽게 할 수 있다.

예를 들면, 어떤 네트 길이 x 3 이라는 네트 길이 규칙을 만들고 싶을 때 이 방법을 이용하면 좋다.

아래 예제에서는 DATA.BD0 와 DATA.BD1의 길이가 DATA.BD2의 3배가 되도록 설정한다.

작업의 편의를 위해 해당 네트 색 변경

1. CMrule에서 실제 길이를 출력하기 위해 analyze 시킨다.

2. Formula를 넣고자하는 부분에 마우스우클릭 - Formula

3. 엑셀처럼 어떤 셀을 누르면 해당 셀의 syntax가 박스에 자동으로 들어간다.

4. 이제 x3배이므로, *3을 뒤에다 입력한다.

5. 3배가 된 값이 해당 칸에 들어감을 알 수 있다.

이 방법으로 원하는 수식값을 넣어서 길이 계산이 가능하다.

아래동영상을 참고했다. (영문)

www.youtube.com/watch?v=l5bqh3qTarA

이 옵션은 Allegro PCB Designer 옵션있어야 사용 가능하다. (OrCAD PCB professional 사용 불가)

보통 PCB에서 Net는 OrCAD Capture에서 Netlist로 넘겨 생성되는 Netlist로 PCB설계를 진행한다.

그러나 그냥 PCB Editor를 열면 Netlist가 없기 때문에, Net정보 또한 없다.

아래 처럼 원하는 net를 만들 수 있다.

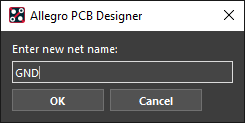

1. Logic - Net logic

1. Options - Create

2. 원하는 Net이름 입력

(테스트)

그럼 추가된 GND를 부여한 Shape을 만들어본다.

할당된 Net를 지우고 다른 Net를 할당하는 방법은 아래에...

ansan-survivor.tistory.com/469

[PCB Editor] Cadence Allegro PCB 에서 네트(Net) 임의로 변경하기

이 기능은 Allegro PCB Designer이상의 옵션이 있어야 사용가능하다. (OrCAD Professional 라이센스로 사용 불가) 회로 설계에 대한 도면이 없고, Netlist도 없을 때 PCB상에서 Net를 수정할 필요가 있을 때, 아

ansan-survivor.tistory.com