http://www.internex.co.kr/insiter.php?design_file=notice_v.php&article_num=31

[PI] Target Impedence : 인터넥스 자료실

47 SI & PI 방문 세미나 관련 인터넥스 2015-01-09 10,392 46 SI & PI 관련 질문 및 의릐 관.. 인터넥스 2014-04-03 10,325 45 자료 update가 지연되는 점 거.. 인터넥스 2011-12-07 14,564 44 광고성 덧글은 임의로 삭제.. 인터넥스 2011-06-20 16,627 43 질문 또는 의견 연락처 인터넥스 2011-06-20 12,100 42 Sample Post-Analysis 결과서(3)

www.internex.co.kr

위 링크를 참조했다.

요약하자면,

1. 임피던스는 최대한 낮은게 이상적. (현실은 그렇지 않음)

2. 보드 작동 범위내 허용하는 노이즈(동작이 가능)를 감안.

3. 그 동작가능 범위 내에서 임피던스를 맞춤. (타겟임피던스 이하)

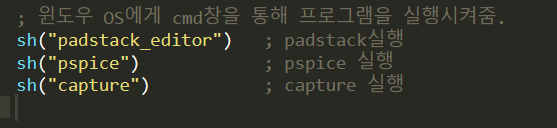

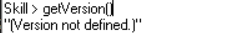

아래 자료는 Pspice를 통한 Target impedance맞추기 시뮬레이션

https://ansan-survivor.tistory.com/443

타겟 임피던스를 맞추기 위한 Decoupling Capacitor(디캡) Pspice 시뮬레이션

타겟 임피던스는 아래 참고, 이를 맞추기 위해 시뮬레이션을 진행했다. ansan-survivor.tistory.com/174 Target Impedance(타겟 임피던스)란? http://www.internex.co.kr/insiter.php?design_file=notice_v.php&ar..

ansan-survivor.tistory.com

'전기전자공부 관련' 카테고리의 다른 글

| ODB++ 란? (PCB 가공에 필요한 CAM 데이터) (0) | 2020.05.15 |

|---|---|

| SMD/SMT 관련 약어들 (저항, 캐패시터, 인덕터 SMD사이즈 0402, 0603, 1005, 1608 등등) (0) | 2020.05.08 |

| 네트워크 / 프로토콜 / 케이블 / RF 관련 IT용어정리 (0) | 2020.03.28 |

| IPC란? (Institute for Printed Circuits) 국제전자산업표준협회 / PCB Footprint 설계 기준 (0) | 2020.03.27 |

| PCB Gerber file 포맷 'Gerber RS274X'에 대해서 (0) | 2020.03.25 |