OrCAD Capture 로 회로도면을 설계하다보면 한 도면 내 모든 회로정보를 다 넣을 수는 없을 것이다.

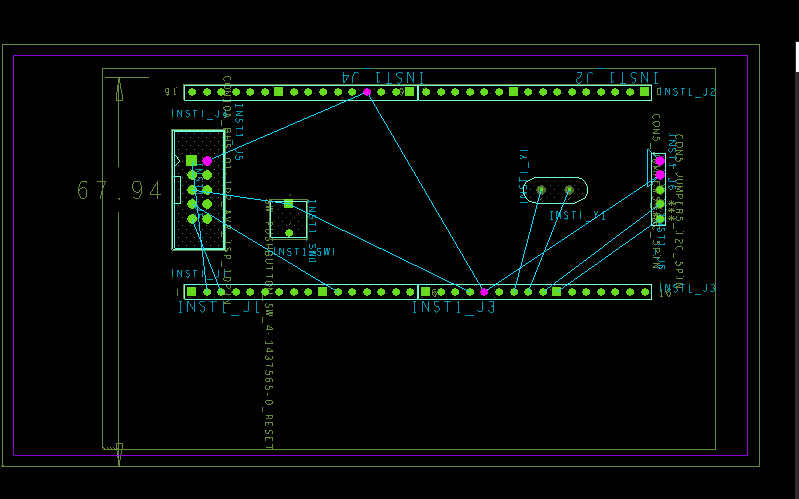

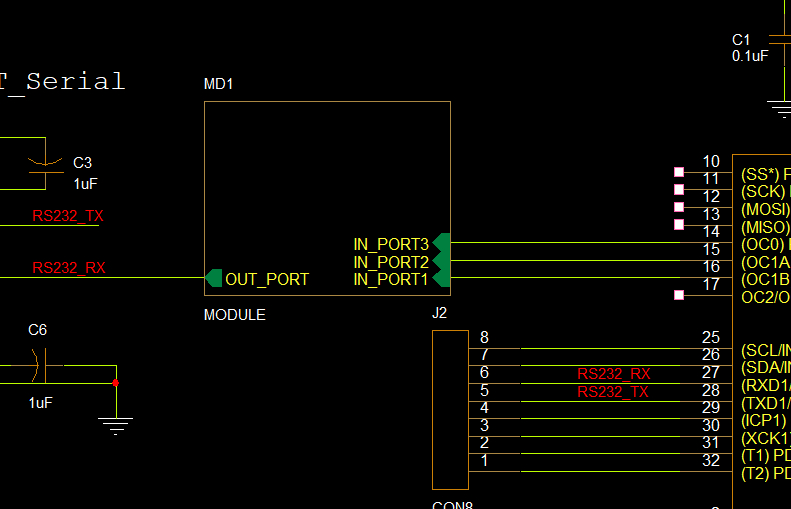

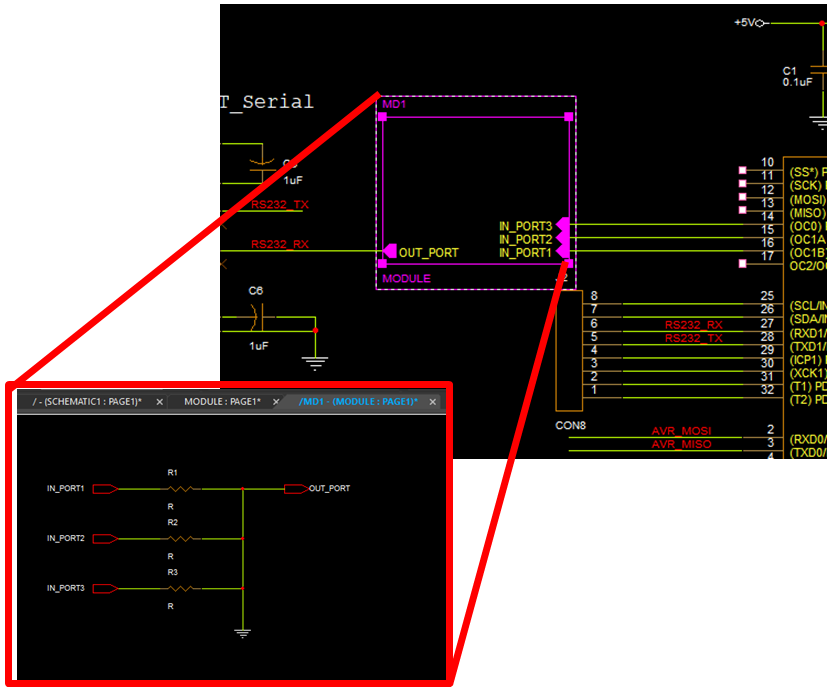

아래와 같이 Main 도면 내에 블록계층을 만들고 해당 블록에 접속할 수 있도록 만들면 편리하다.

OrCAD Capture에는 hierarchical Block 설계를 지원한다.

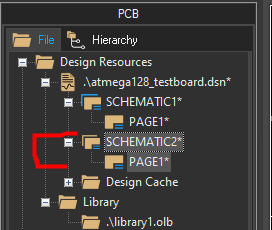

그러기 위해서는 먼저 도면의 Tree 구조를 만들어야 한다.

다른 회로도의 계층구조블록(hierarchical Block)을 만드려면 다른 Schematic Page가 필요하다.

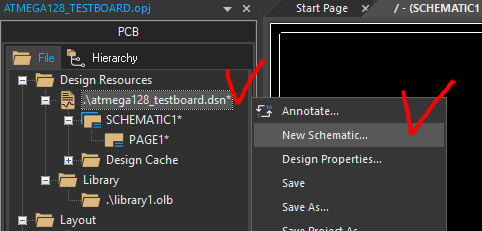

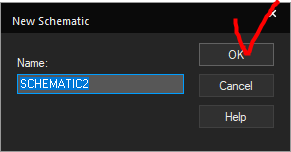

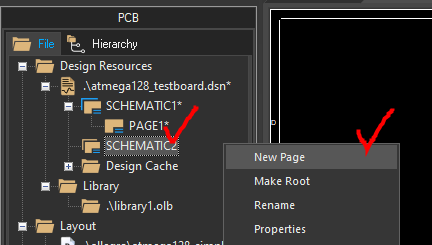

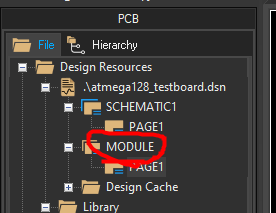

< 계층 블록을 사용하기 위한 Schematic Tree 구조 만들기>

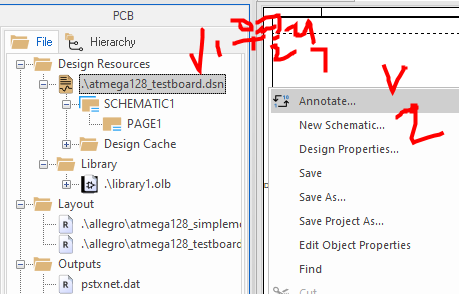

1. 최상위 트리인 xxx.dsn 파일 마우스우클릭 - New Schematic

2. 새로운 schematic에서 새로운 page 만들기

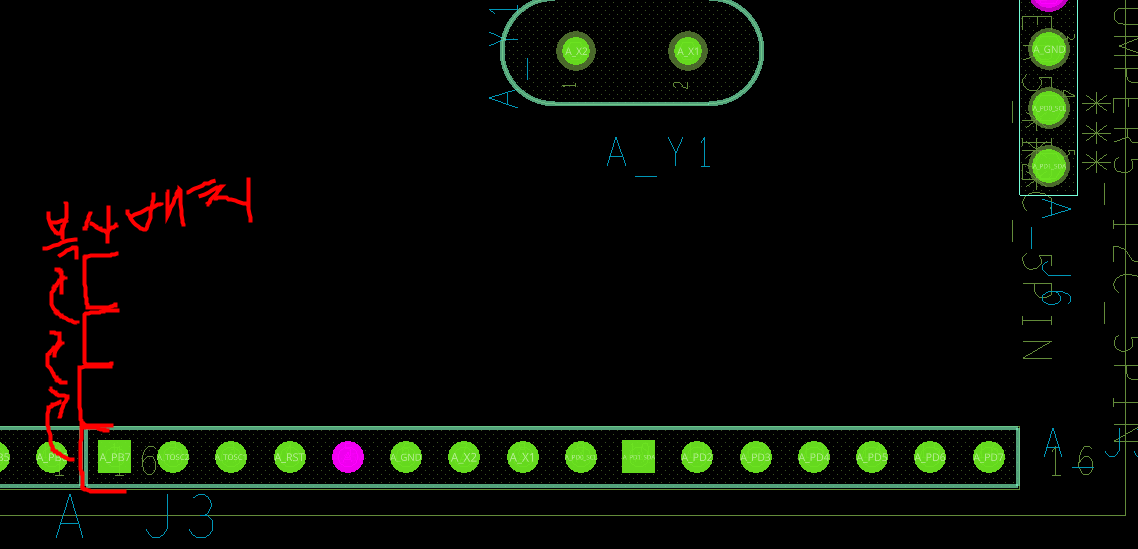

아래와 같이 main 회로도도와 다른 Schematic 트리에 만들어야 모듈로 사용할 수 있다.

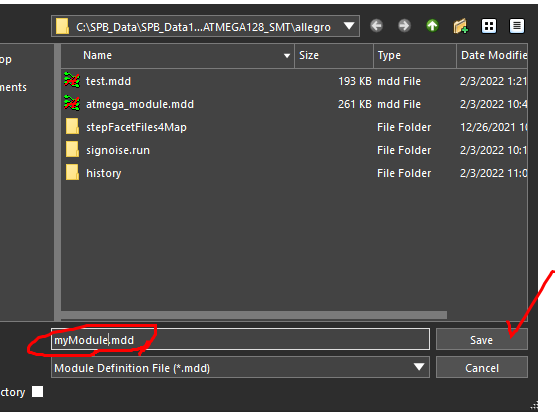

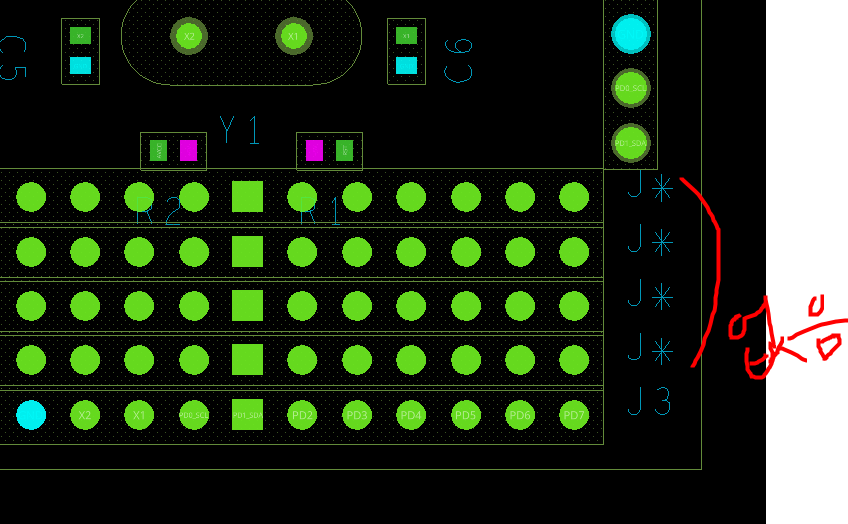

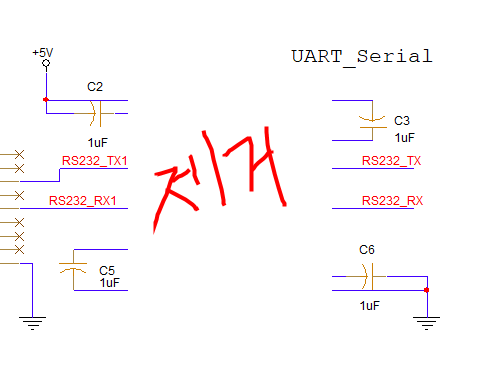

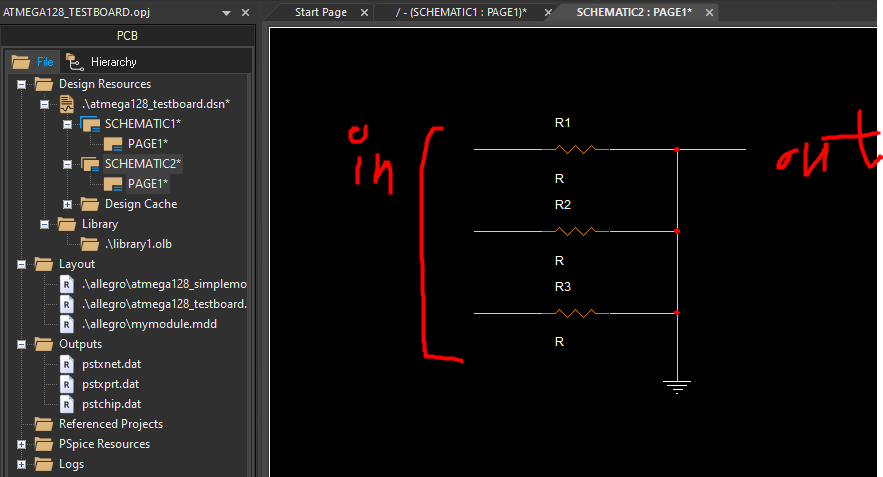

3. 모듈 회로도 만들기

4. 회로도에 IN/OUT 포트 만들기

4-1. IN 포트 만들기 (모듈 회로도로 들어오는 포트)

4-2. OUT 포트 만들기 (모듈 회로도에서 나가는 포트)

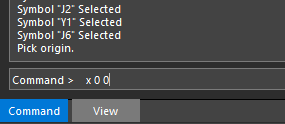

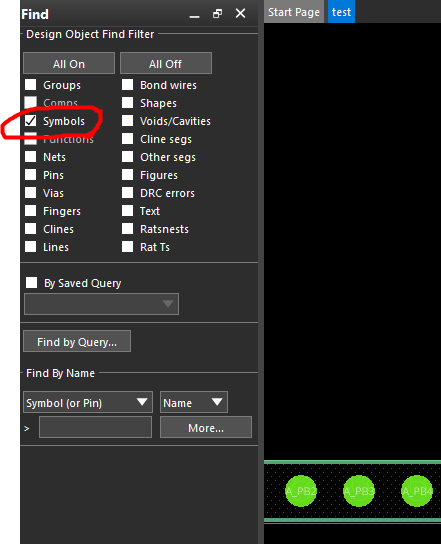

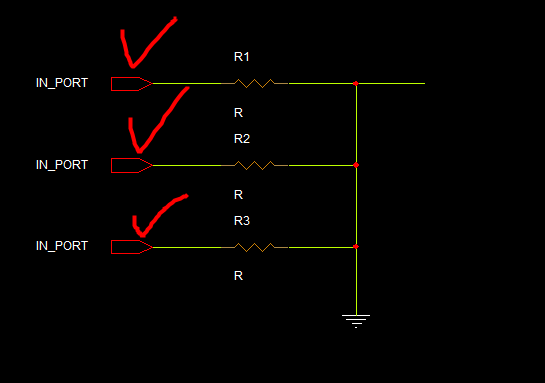

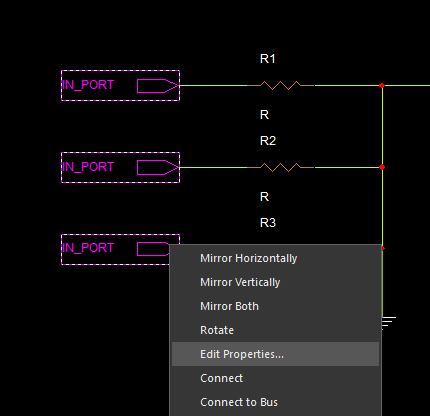

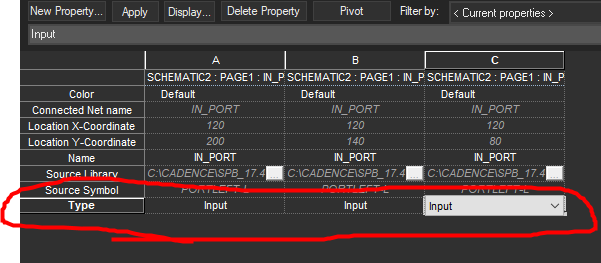

5. 포트에 Properties 지정하기 (동일한 Net가 아닌 이상 포트 이름이 각각 달라야 한다 )

Pivot으로 보기 편하게 변경하고, Type을 본다. Default로 Output으로 되어있는데, Input으로 사용할 항목은 다 변경시킨다.

6. 적당히 Rename으로 이름을 변경해준다. (모듈에서 불러오기 편하도록)

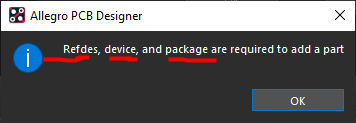

< Main 회로도에서 계층 블록(Hierarchical Block) 회로도 불러오기>

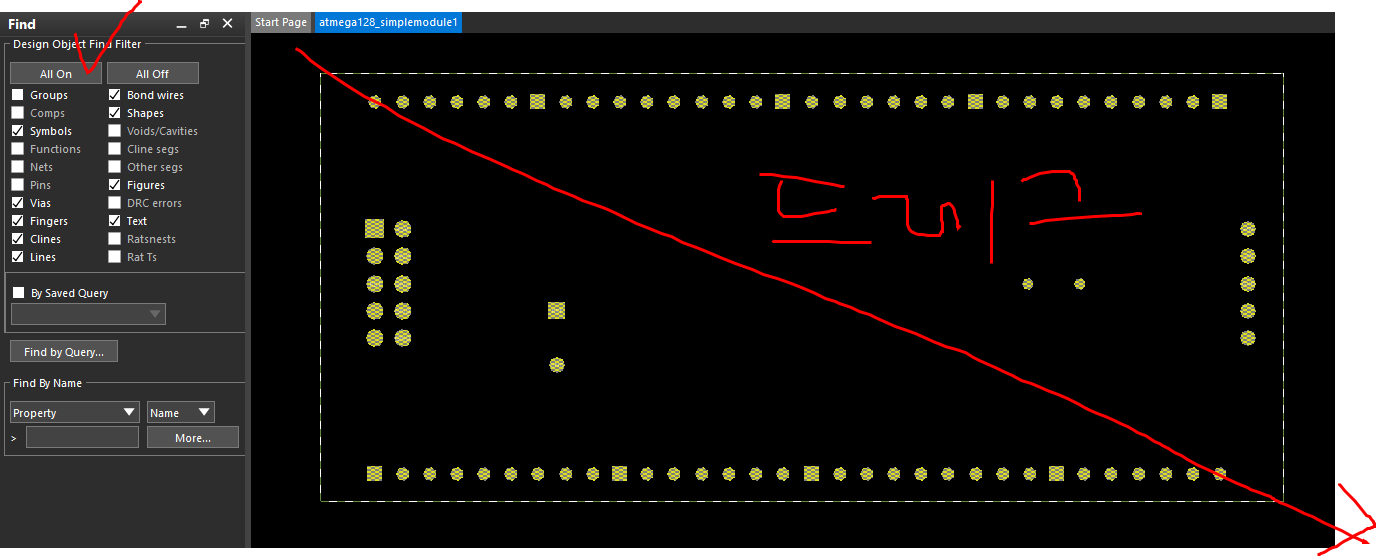

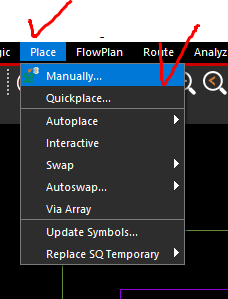

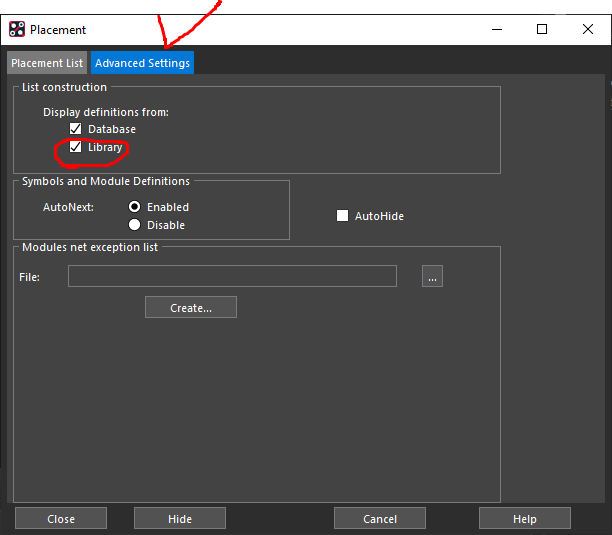

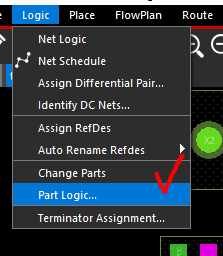

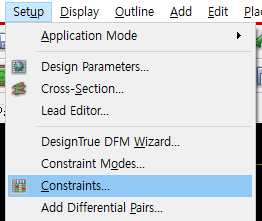

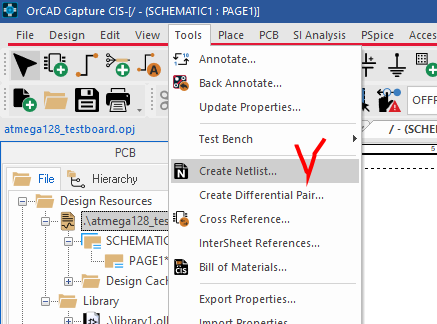

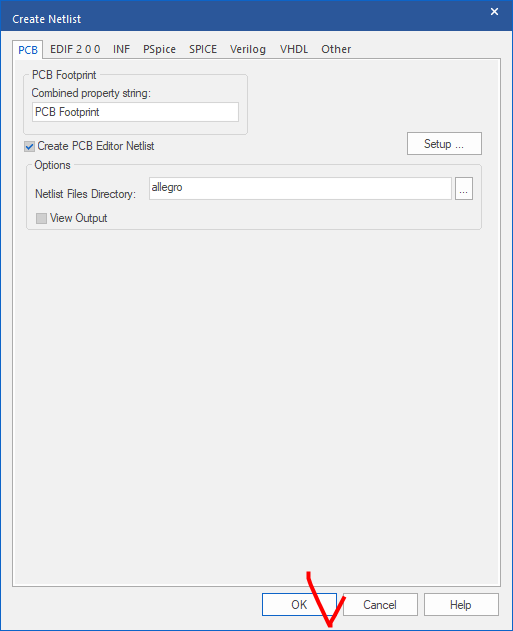

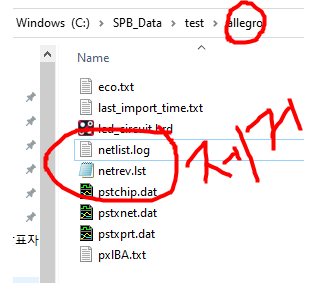

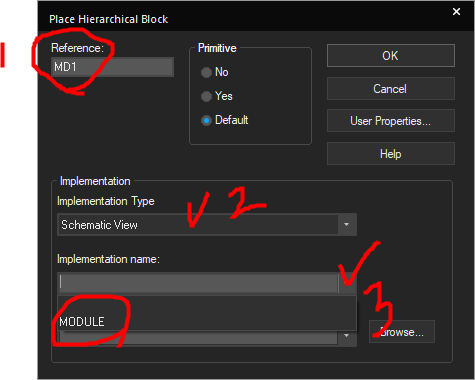

1. place - Hierarchical Block

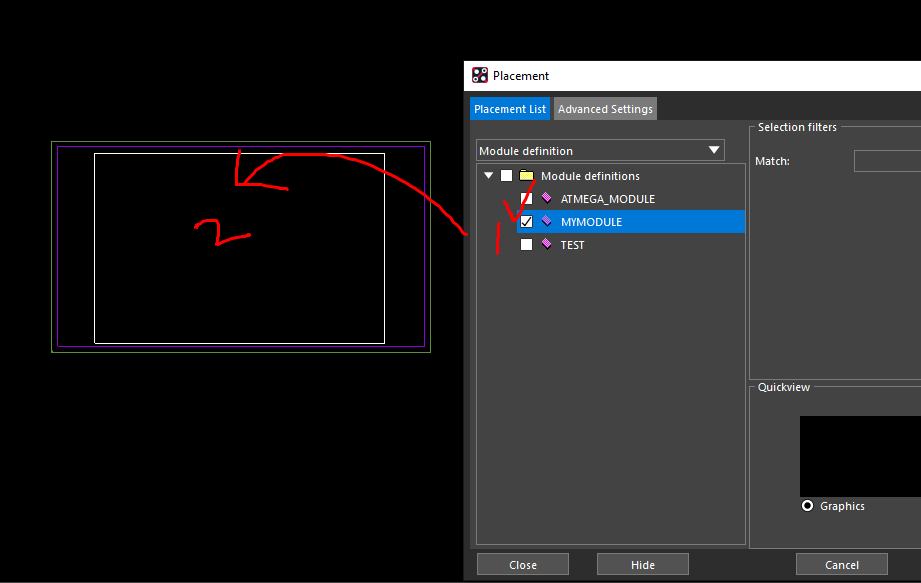

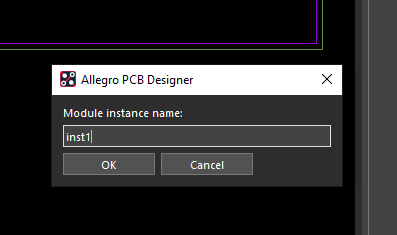

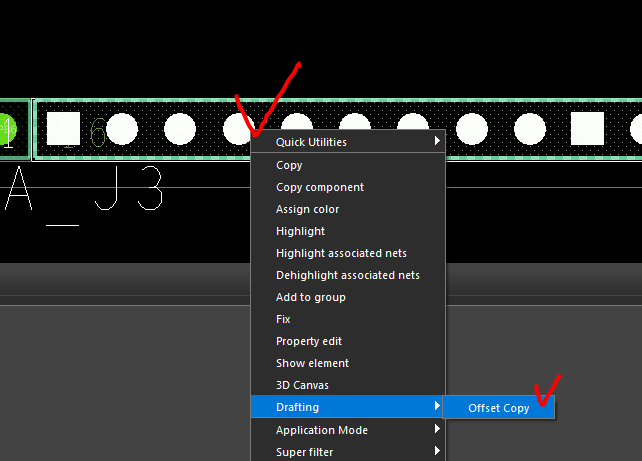

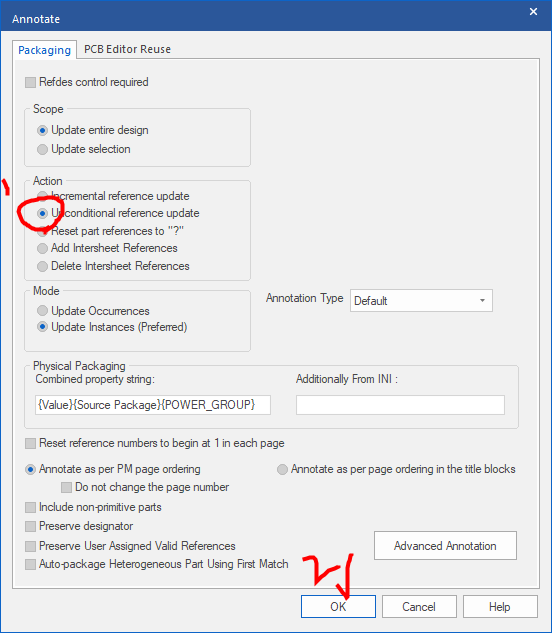

2. Reference를 작성 - Schematic View 변경 - 하위 목록으로 아까 만든 MODULE 회로도를 선택

(모듈이므로 여러개를 복사해서 만들 수 있다. 각 모듈마다 Reference 번호가 매겨진다. 뒤에 숫자 1을 넣으면 복사할 때마다 증분된다.)

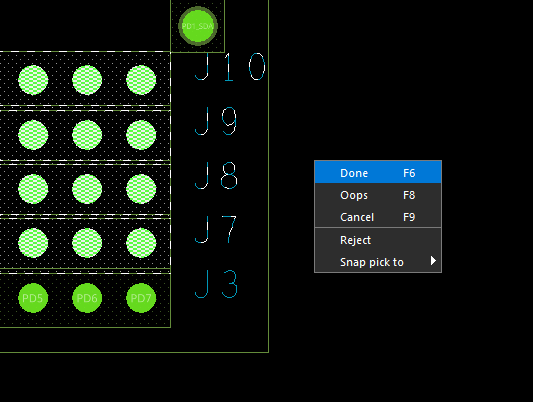

3. OK를 누르면 마우스가 '십자기' 형태로 변한다. 이때 회로도에 드레그만 해주면 생성된다.

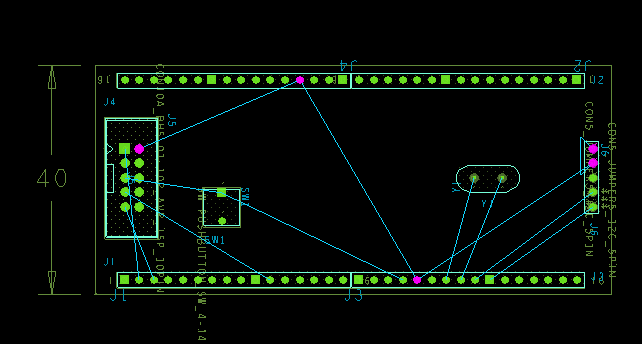

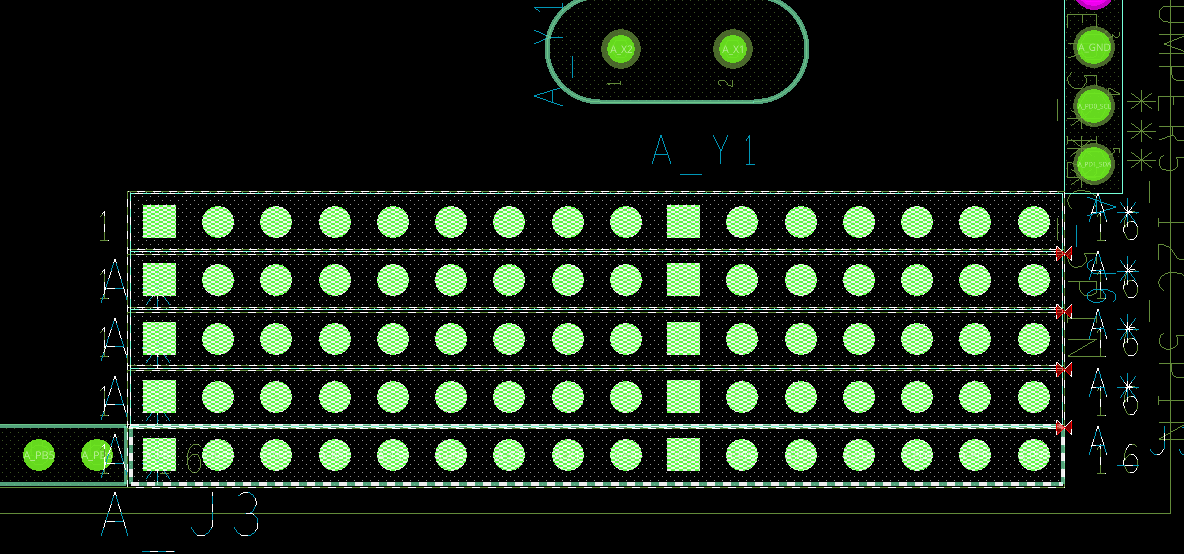

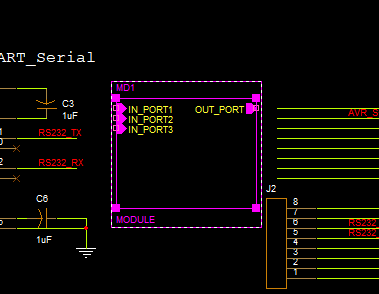

(결과)

회전하고(단축키 R) 반전하고(단축키 V 또는 H) 등등 다 먹힌다. 이제 메인의 회로도에 하위 계층 블록으로 배치가 된 것이다.

해당 모듈을 복사 붙여 넣기 하면 똑같은 회로도가 여러개 생성되는 것이다. 또한 그 모듈에 대한 Reference 가 증가함을 볼 수 있다.

해당 모듈 블록을 더블클릭하면 하위 계층 도면으로 이동할 수 있다.

(계층구조 Hierarchical block을 라이브러리 화 시키기 .OLB 파일로 변경)

https://ansan-survivor.tistory.com/586

[CAPTURE] OrCAD Capture 계층블록(Hierarchical Block)을 라이브러리 파일(.OLB 파일)로 변경시켜 설계 재활용

* 계층구조(Hierarchical Block)에 대해서 모른다면 아래를 참고한다. https://ansan-survivor.tistory.com/1259 [CAPTURE] OrCAD Capture 계층 구조 도면 만들기 ( 계층 블록 하위 도면 hierarchical Block) OrCA..

ansan-survivor.tistory.com

(계층 구조가 아닌, 다른 페이지에 Net를 연결하는 방법, off-page)

https://ansan-survivor.tistory.com/1261

[CAPTURE] OrCAD Capture 다른 페이지 Net 연결하기 (Off-page 연결)

OrCAD Capture에서 회로도의 화면이 부족할 경우, 다른페이지로 Net를 연결할 수 있다. 이때 Off-page 포트 기능을 사용한다. Page1에 있는 LED1,2,3 네트를 Page2의 네트에 연결하고 싶을 때 사용. 1. 메인 페

ansan-survivor.tistory.com