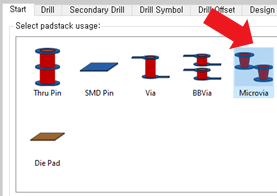

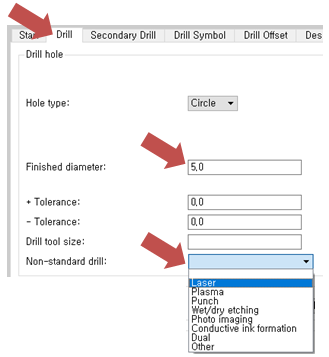

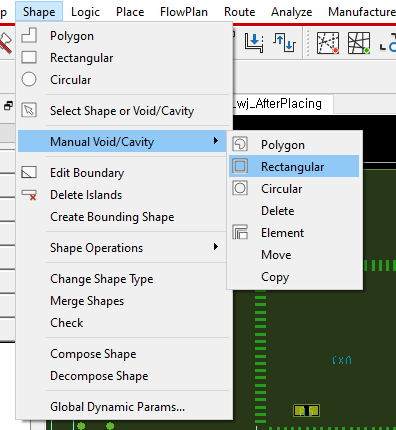

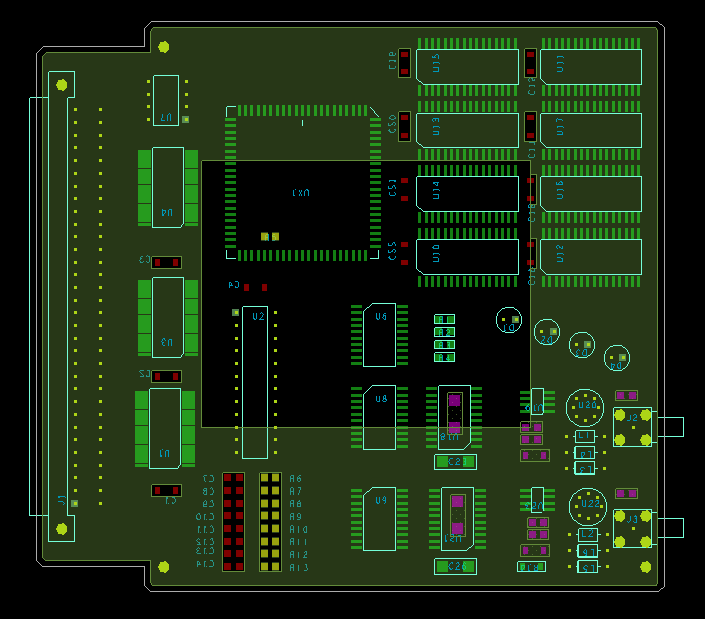

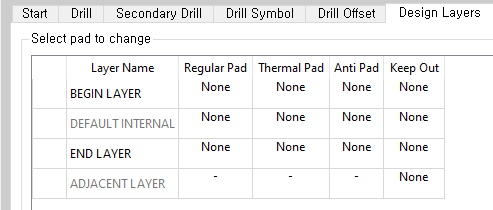

OrCAD에서 제공하는 pad만들 때쓰는 툴인 Padstack에는 다음과 같은 pad메뉴가 있다.

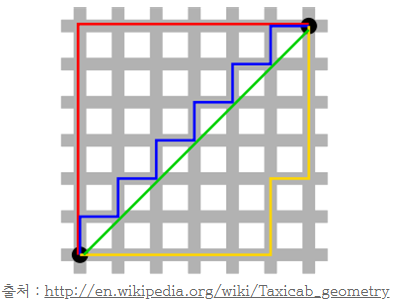

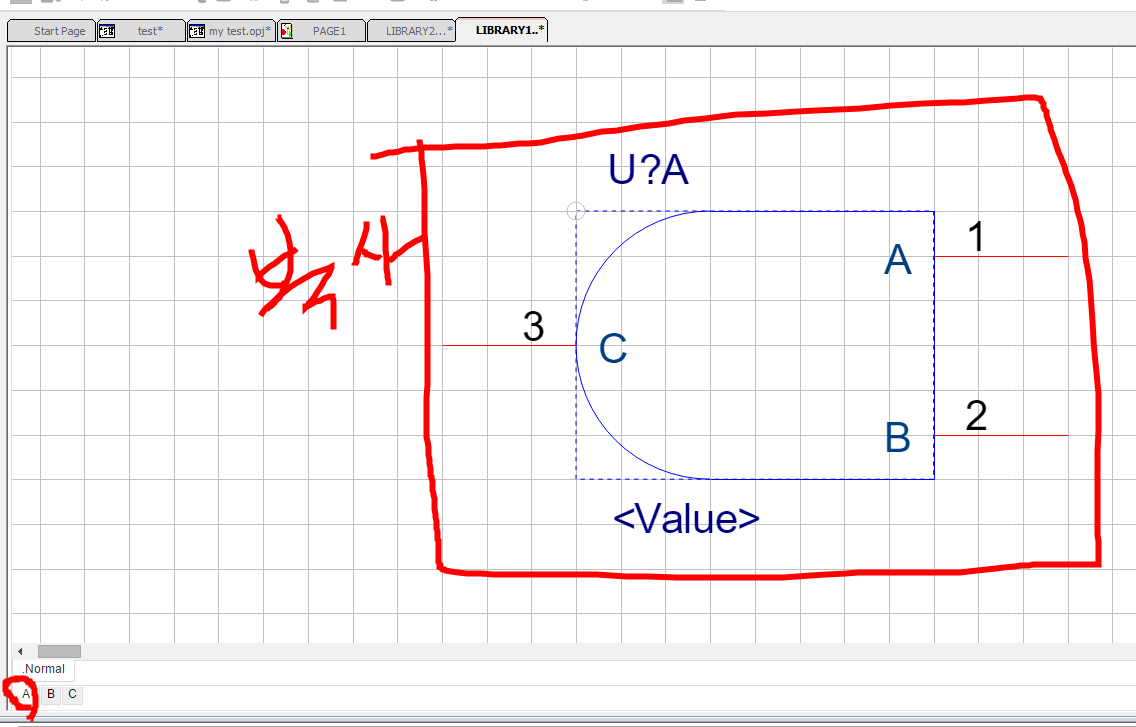

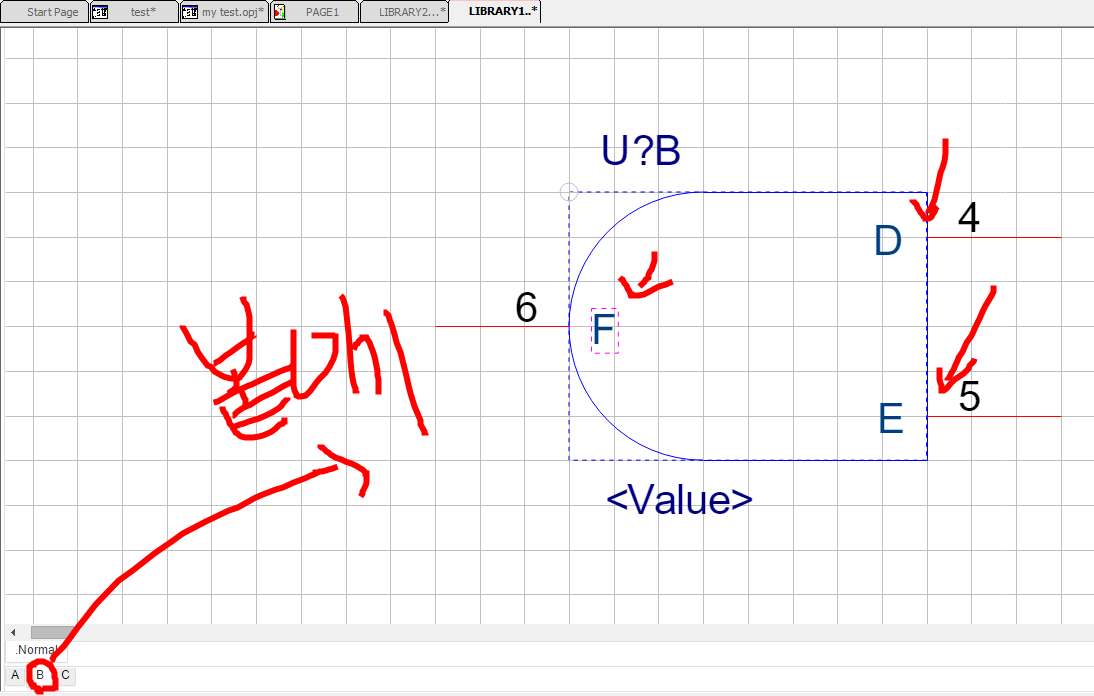

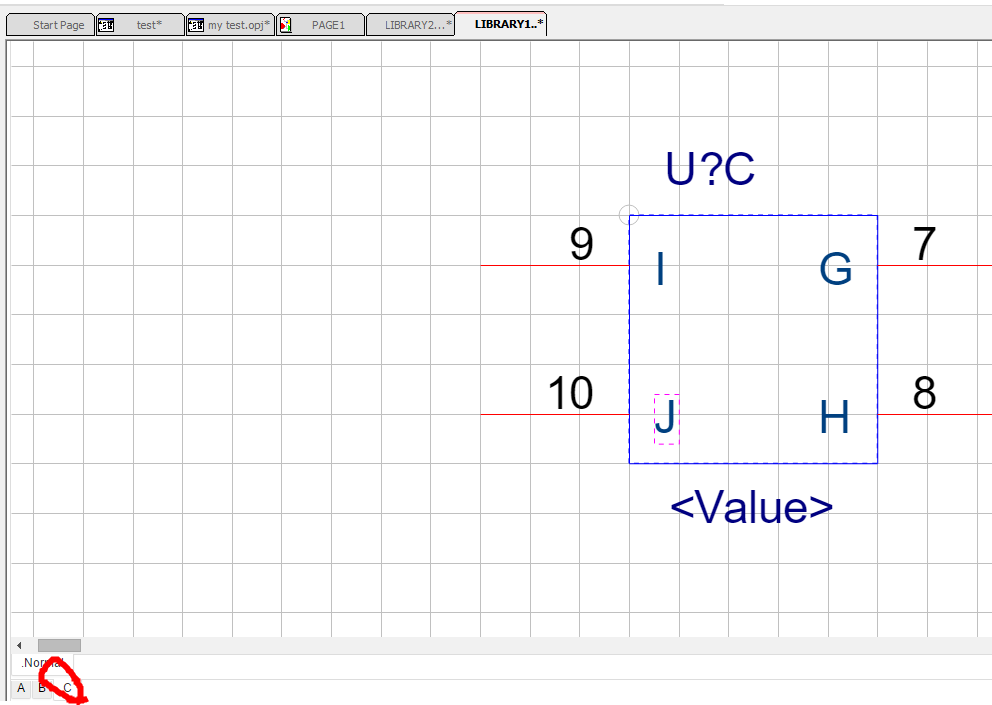

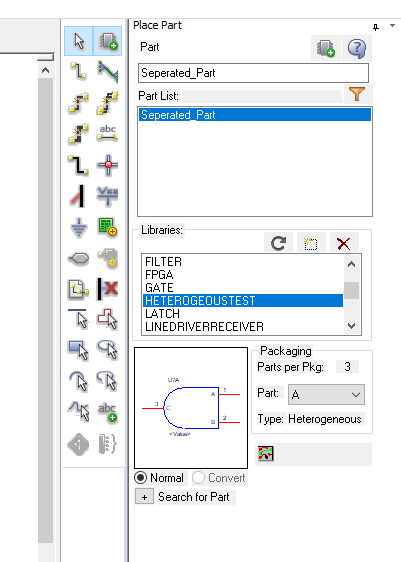

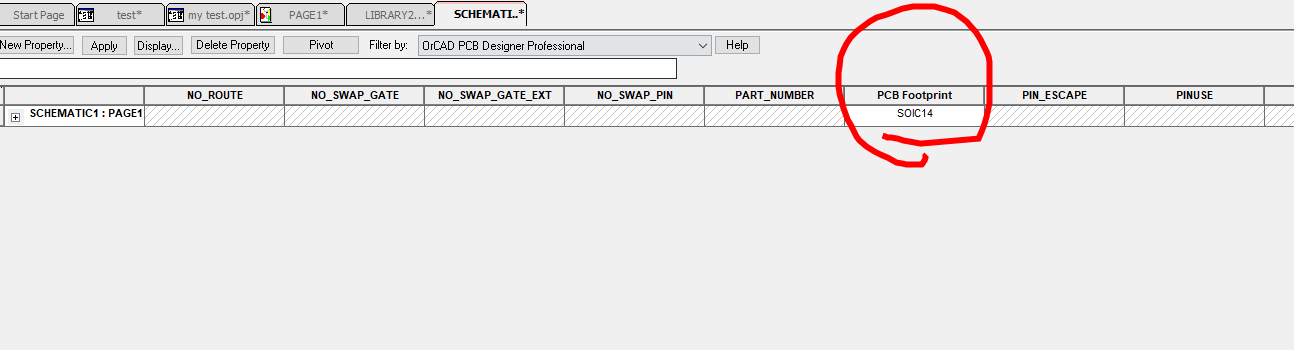

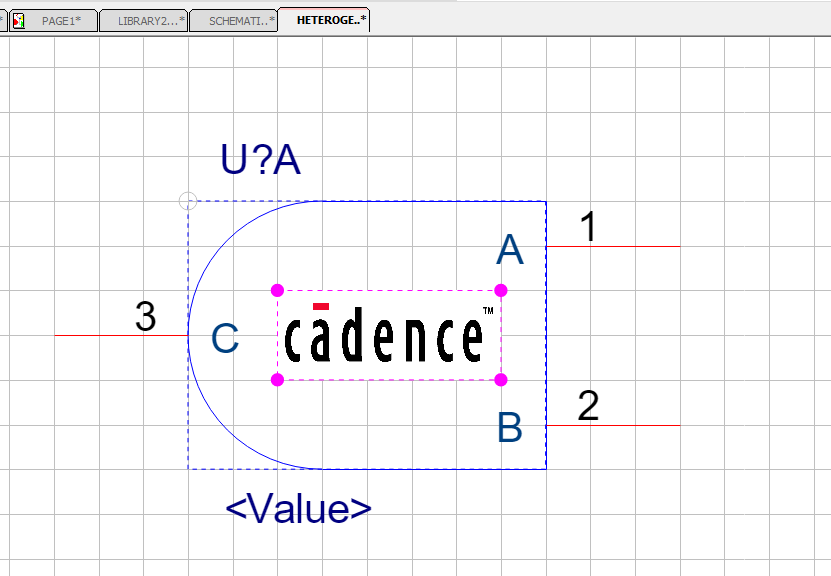

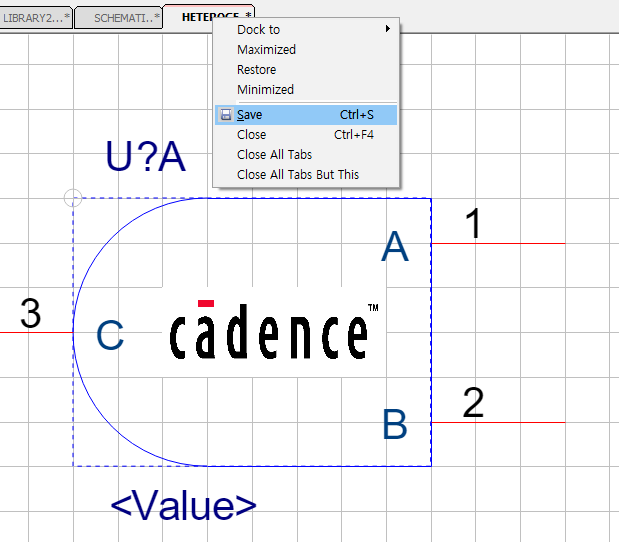

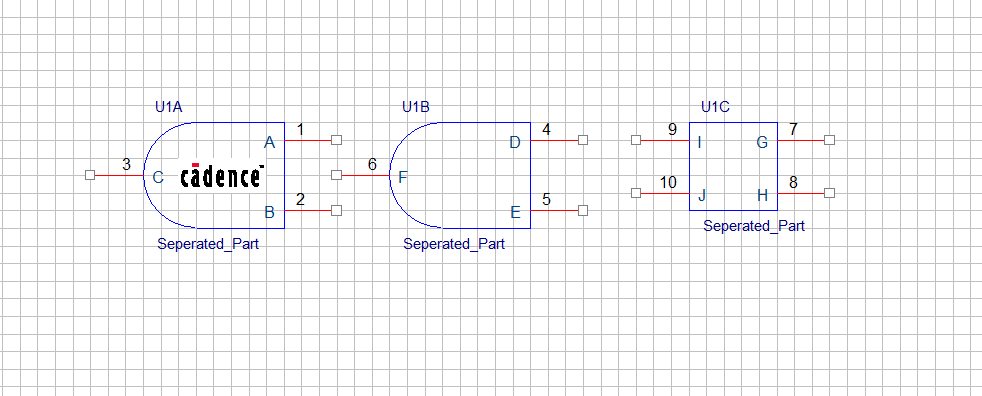

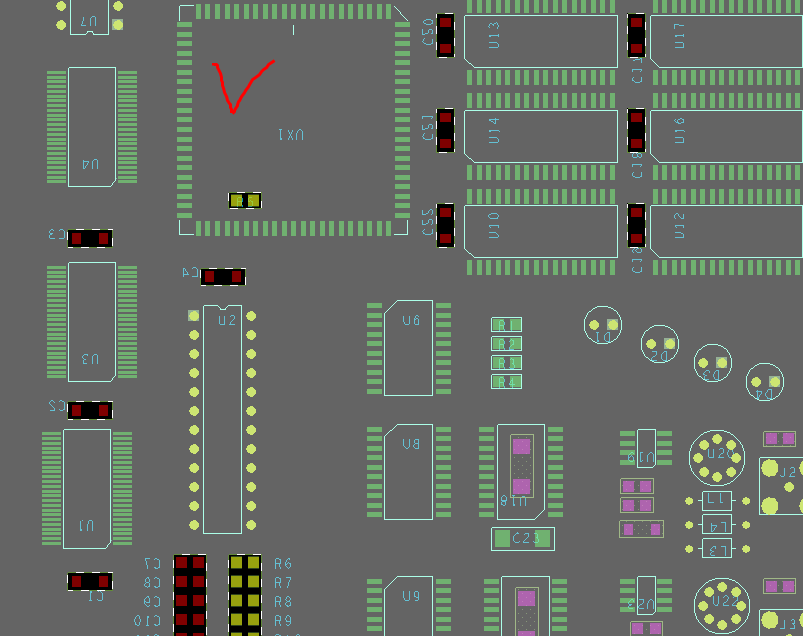

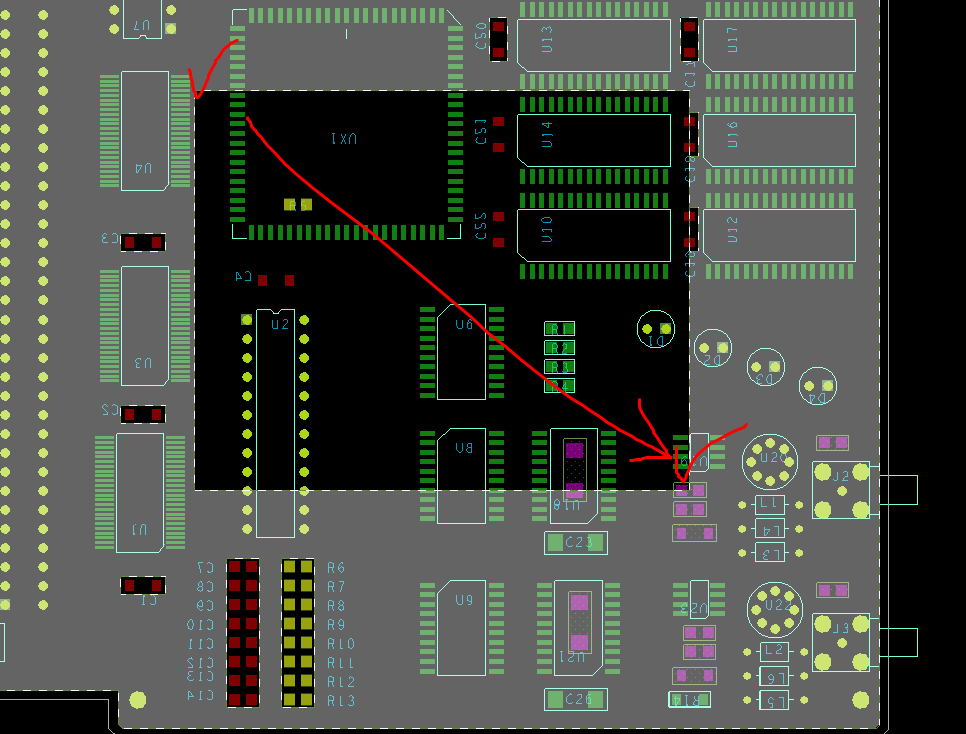

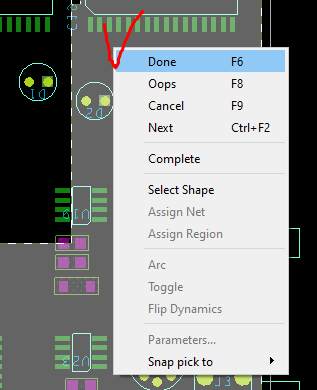

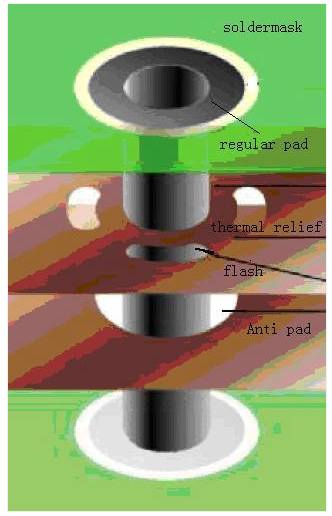

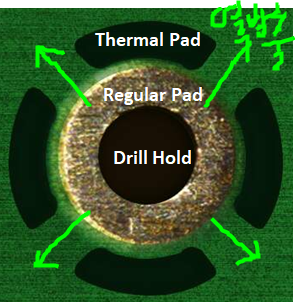

그림먼저 보자면,

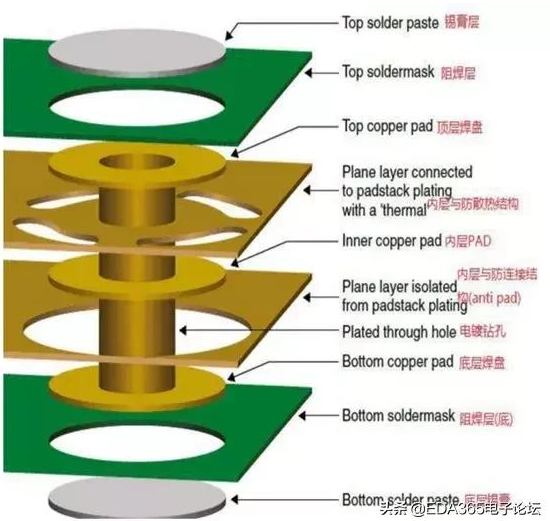

가장 위에 Soldermask는 일반적인 PCB기판의 초록색으로 덮힌 부분 가장 외곽에 씌여진 필름이다.

이름 그대로 Solder가 원하는 부분에만 모여있도록 하는 Mask이다. 즉, 원하는 위치에만 납이 머무르도록 한다. 그 외부분은 납이 묻지 않도록 한다.

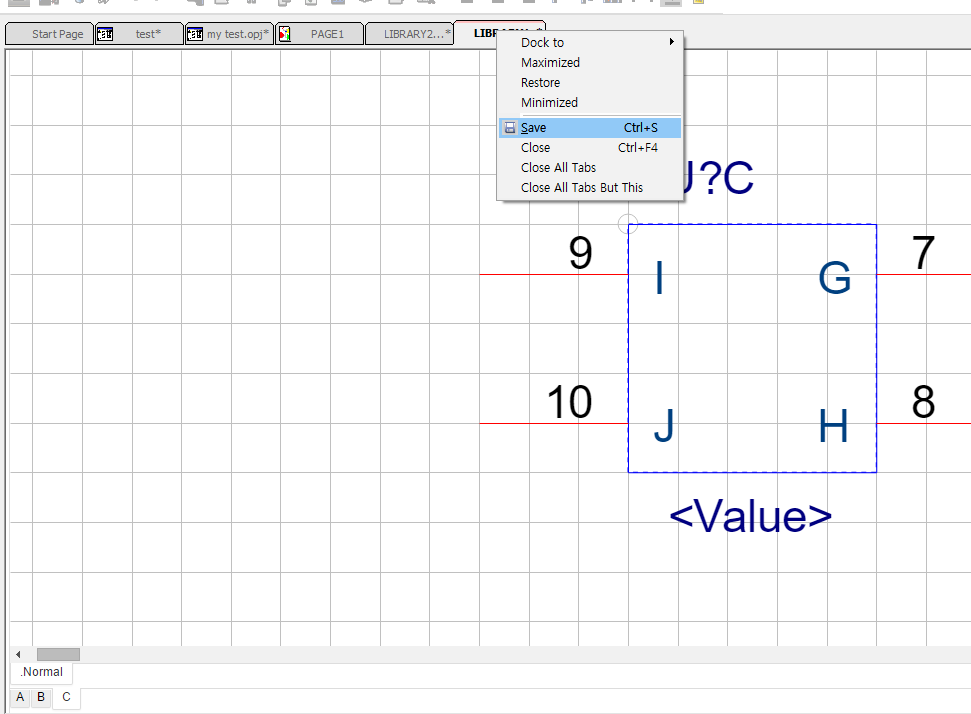

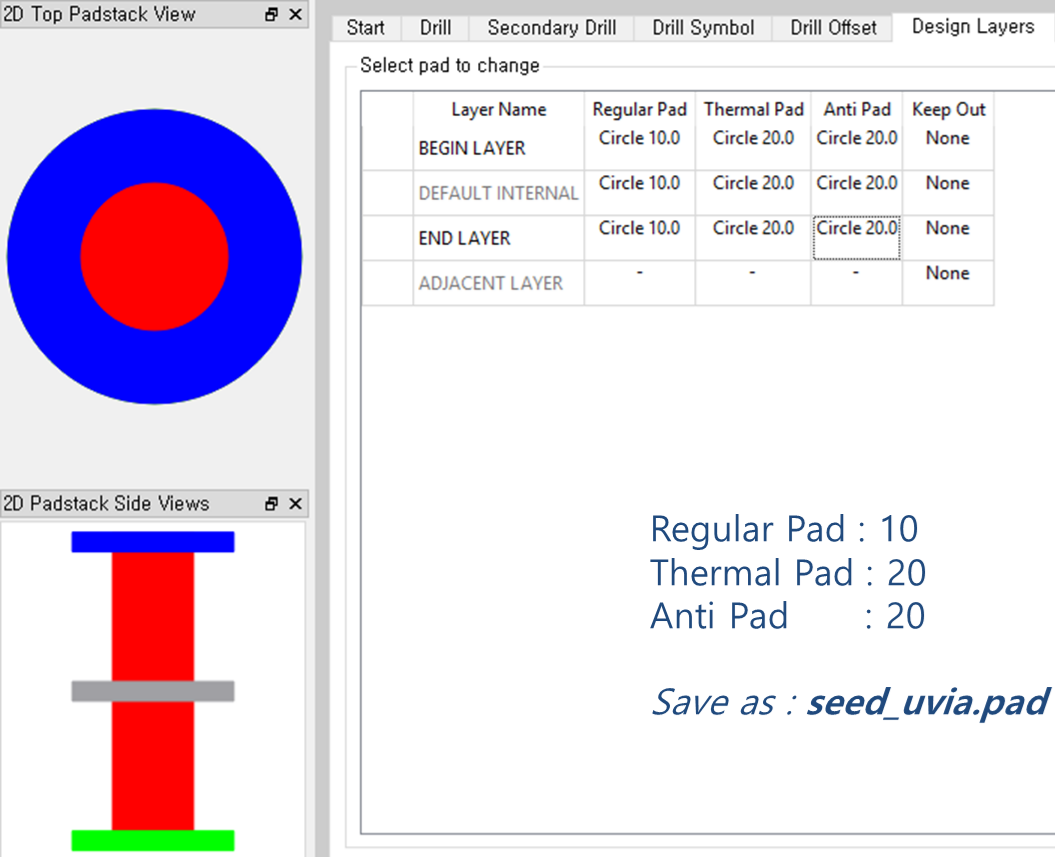

1. Reugular Pad

가장 최상단과, 하단 (Top, Bottom)에 있는 Pad며, 부품의 Pin을 납땜하기 위한 공간. 우리가 쉽게보는 그 pad이다.

2. Thermal Pad

다른말로 Thermal Relief라고도 한다.

넓은 Coppor Plate(Plane Layer = Shape Area) 와 연결되어있는 Pad에 Pin을 납땜할때 (예를들면 GND핀이나 VCC핀)

납땜으로 인하여 발생한 열이 Plane를 타고 다른 부품에 영향을 주지 않도록, 또는 급격하게 방열이 되어 납이 제대로 안되는 것을 방지하기 위한 목적.

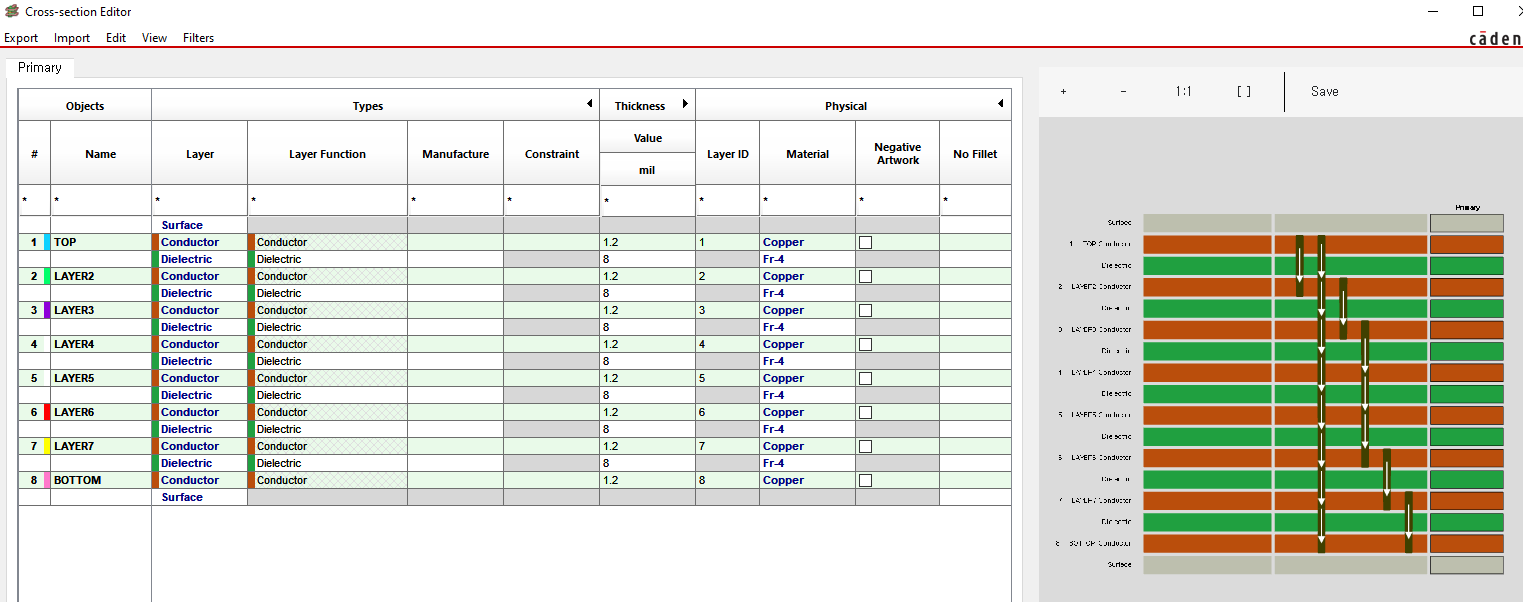

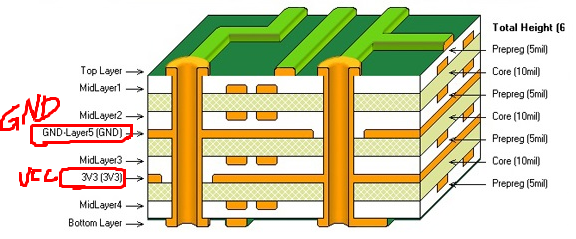

예를 들어, 어떤 Through Hole에 어떤 Pin을 납땜을 한다. 이때 PCB 기판의 Layer는 8층.

저 Hole에 납땜을 하면, GND Plane과 VCC Plane의 동판의 크기가 넓기 때문에, 방열판의 역할을 할 수가 있다.

납땜은 납의 녹는점까지의 충분할 열을 가해야 납이 녹을 수 있는데, 저 동판이 열을 다 빼앗아가면 납땜이 제대로 되지 않는다. 다시말해 냉땜이 될 가능성이 높다는 것이다.

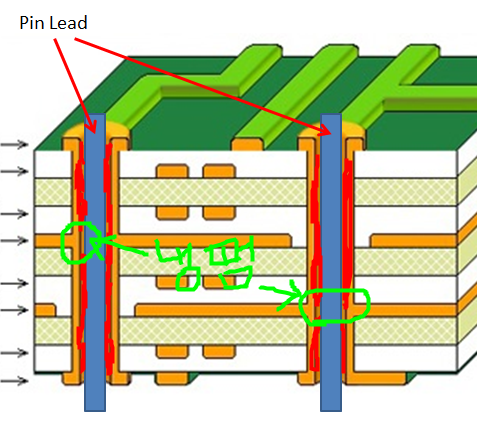

핀의 lead가 Hole전체에 납과 같이 잘 부착이 되어야 하는데, 일부는 부착이 되고, 빨리 식어버리는 부분은 부착이 안되면, 이를 'Bad solder joint' 라고 한다.

그래서 저 Plane과 연결된 부분에 'Thermal Pad (=Thermal Relief)'를 배치해 급격한 열 방출을 막는 것이다.

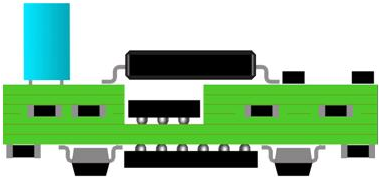

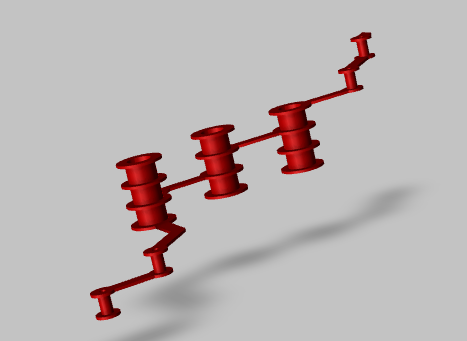

저 4개의 외곽부분에 Void공간 (공백 공간)을 형성하여 열이 빠져나갈 면적을 줄이는 것이다. 즉 모든공간으로 열이 빠져나갔으나, 이제는 저 4개의 연결된 부분으로만 열이 빠져나갈 수 있다.

저 Void가 있는 부분은 우리눈에 보이지 않는다. 왜냐하면 Plane이 있는 layer에 내장되어 있기 때문!

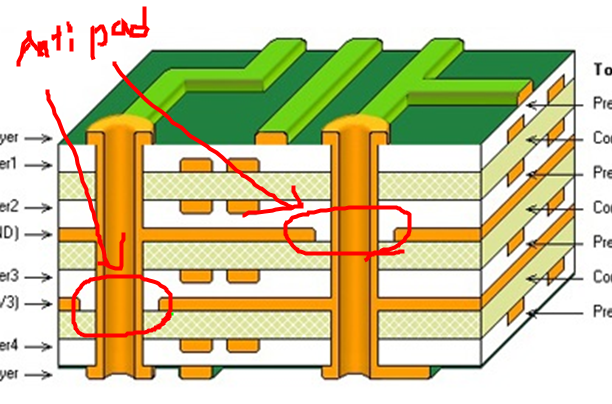

3. Anti Pad

어떤 Through Hole Pad에서 넓은 Coppor Plane (=Shape)과 이격시키는 거리.

예를들어 아래 8 layer 경우 VCC와 GND Plane이 넓게 깔리게 되면, Through Hole핀을 만들 때, VCC, GND 핀이 아닌 경우는 아래 그림과 같이 이격거리를 둬야 한다. (아니면 Short되버리니까, 또는 Capacitance가 발생 우려)

(* layer를 나누는 기준은 동판이 몇층인가)

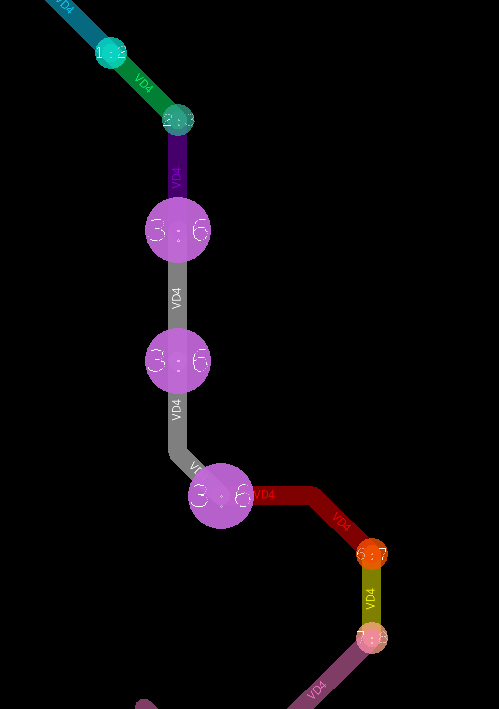

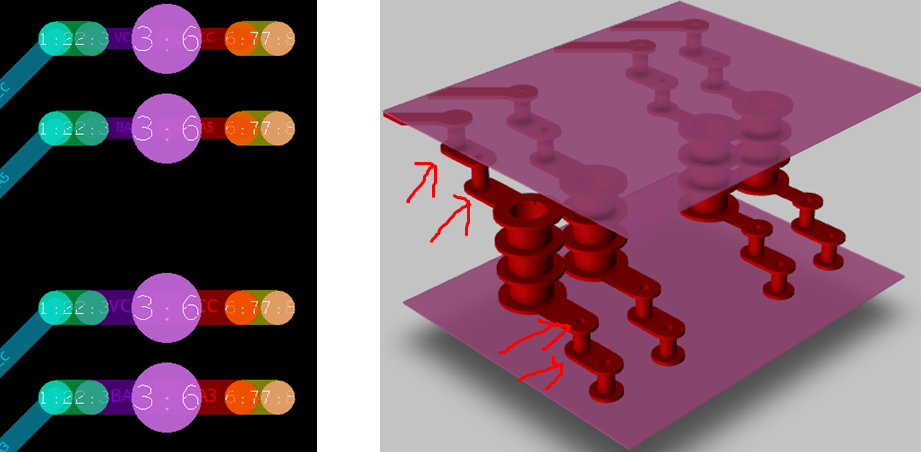

아주 좋은 그림이 있어 추가한다.

* Thermal pad를 보면 4개의 void구멍을 볼 수 있다. 저기는 VCC나 GND로 볼 수 있다.

* Anti pad를 보면 Through hole에서 거리가 이격됨을 볼 수 있다.

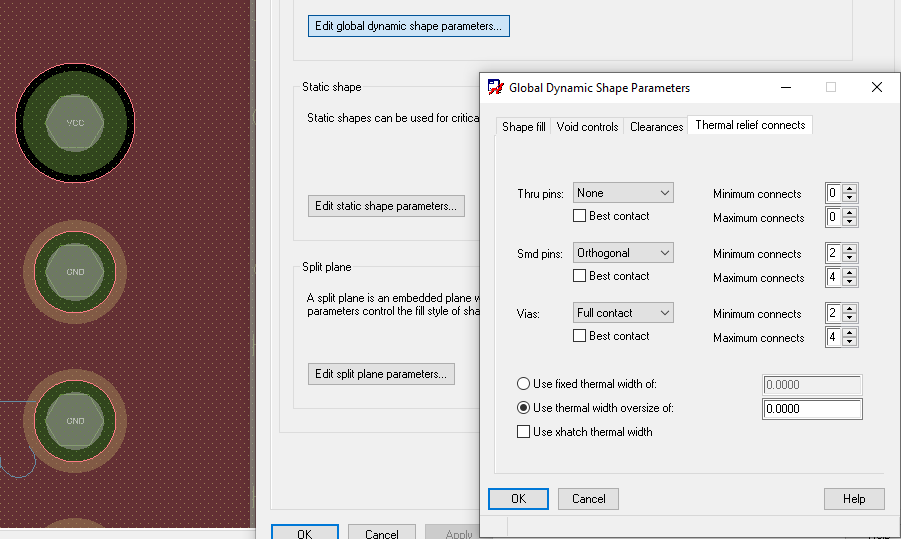

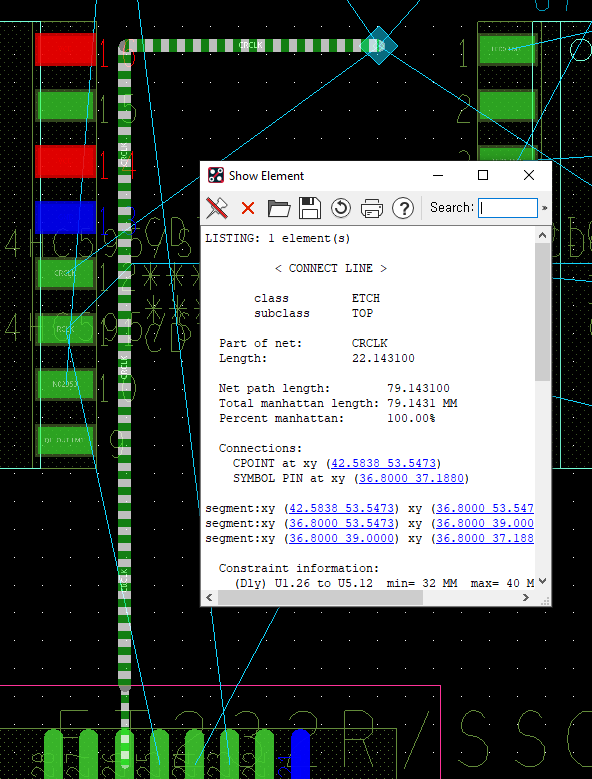

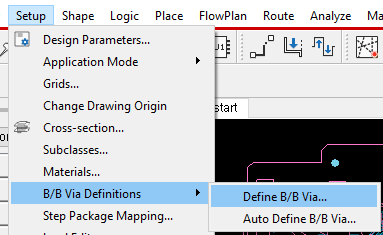

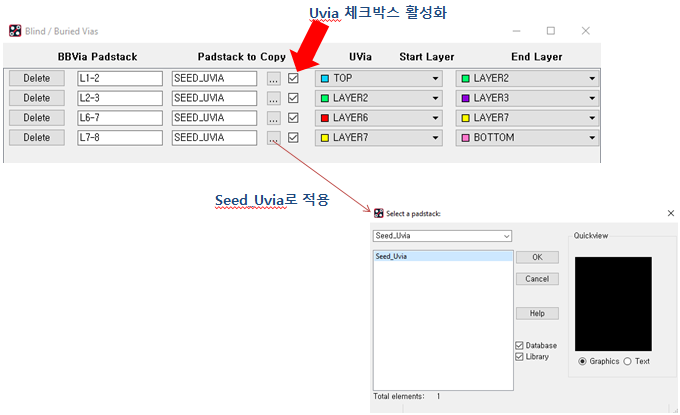

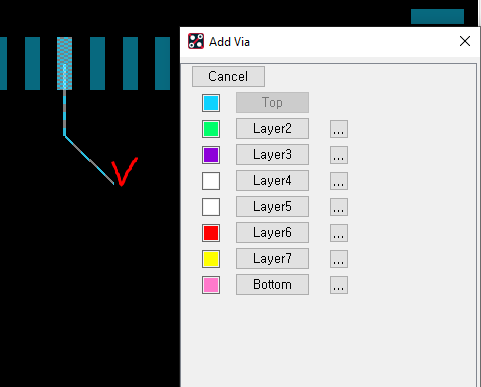

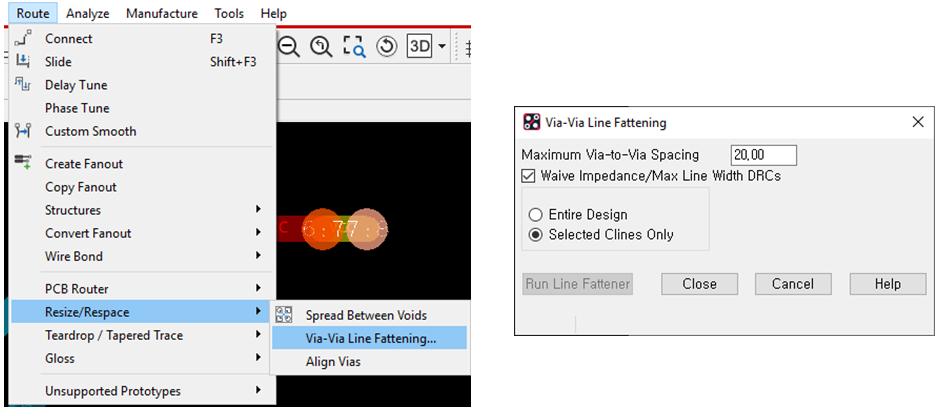

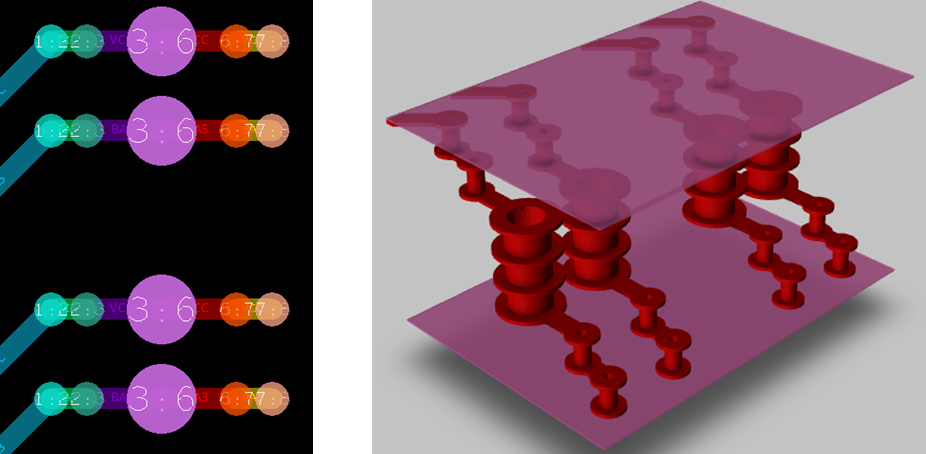

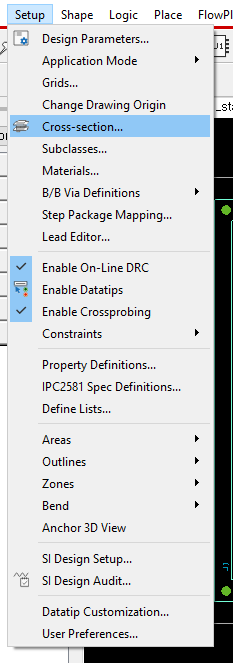

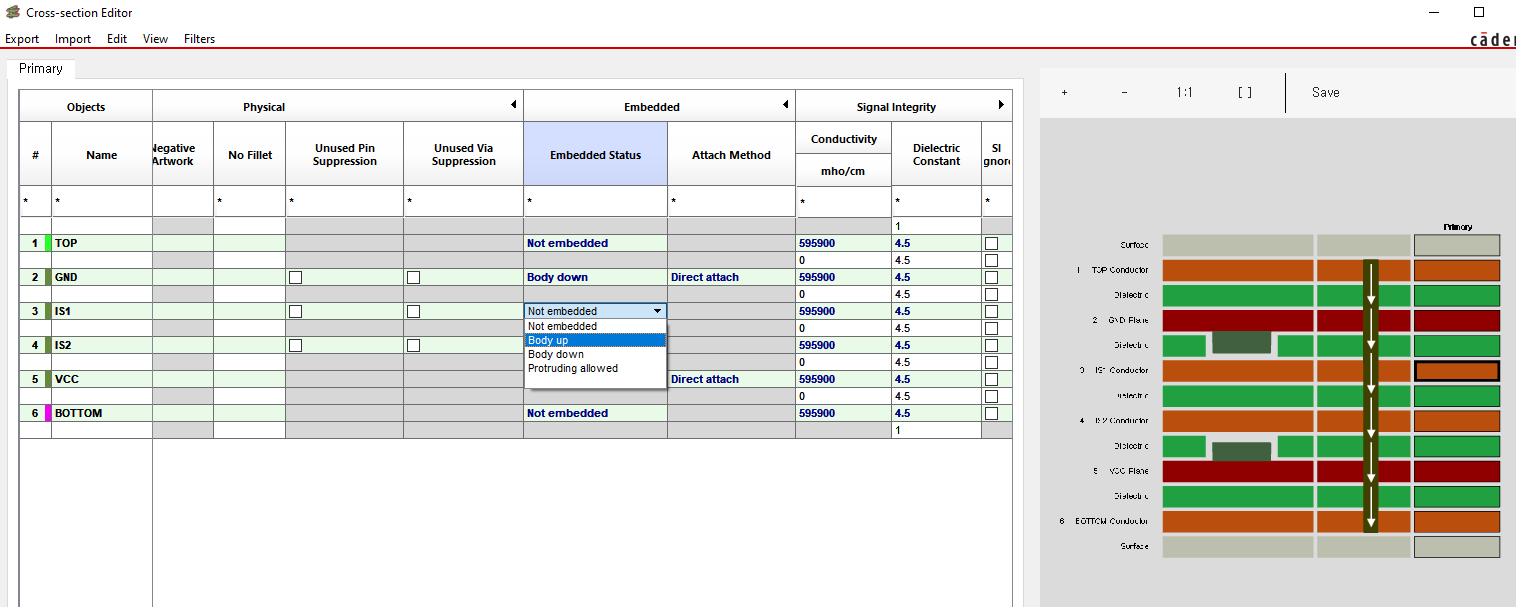

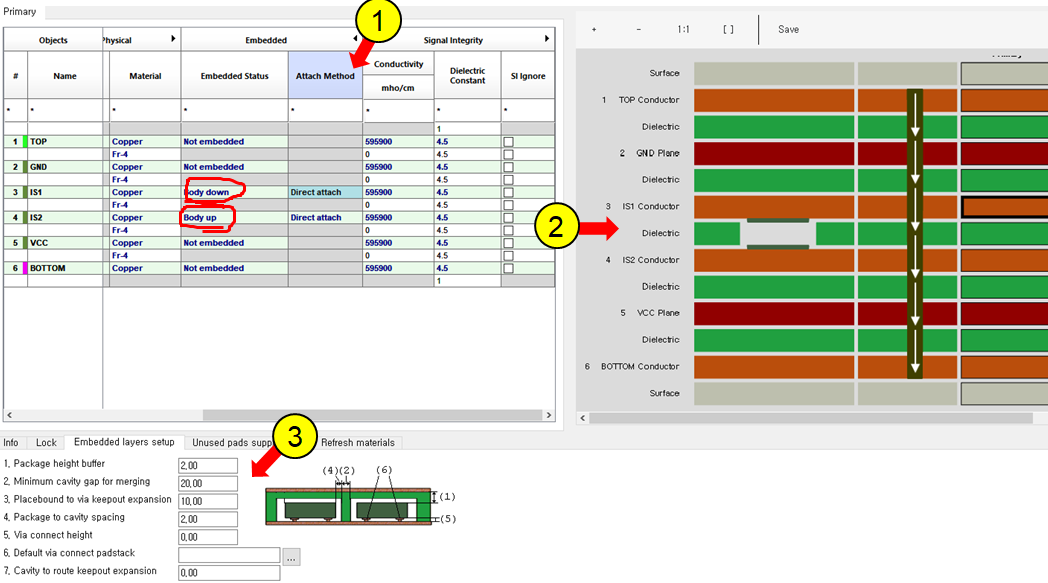

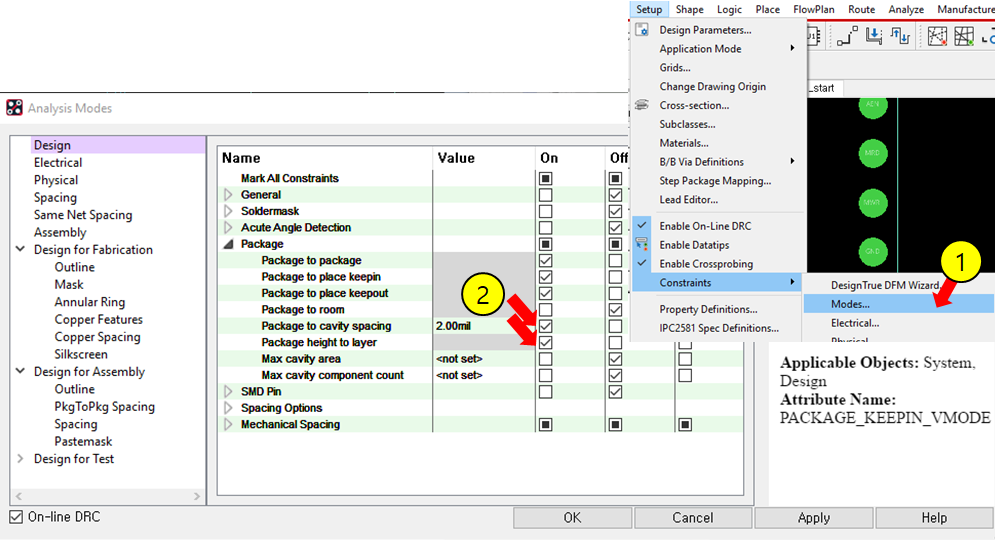

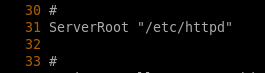

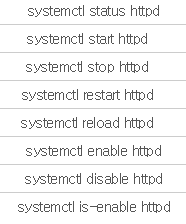

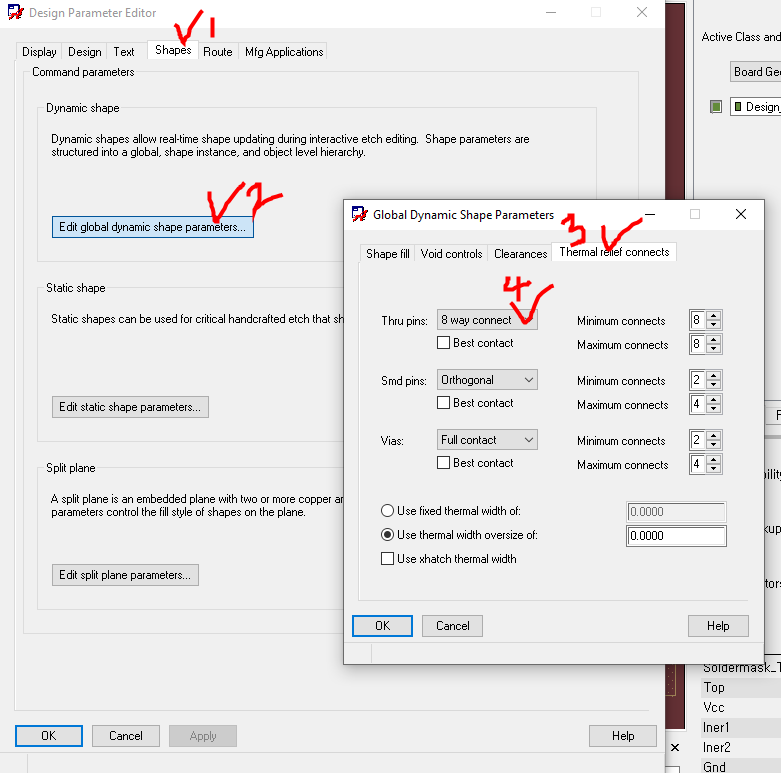

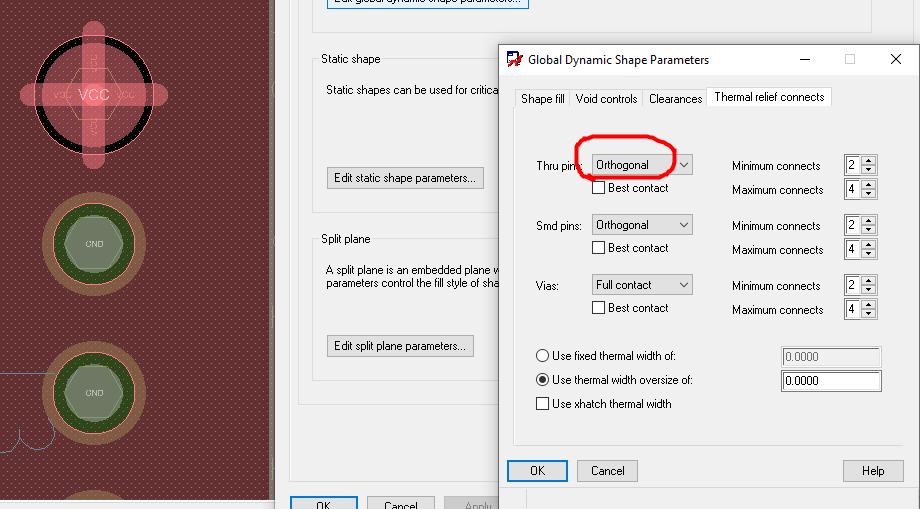

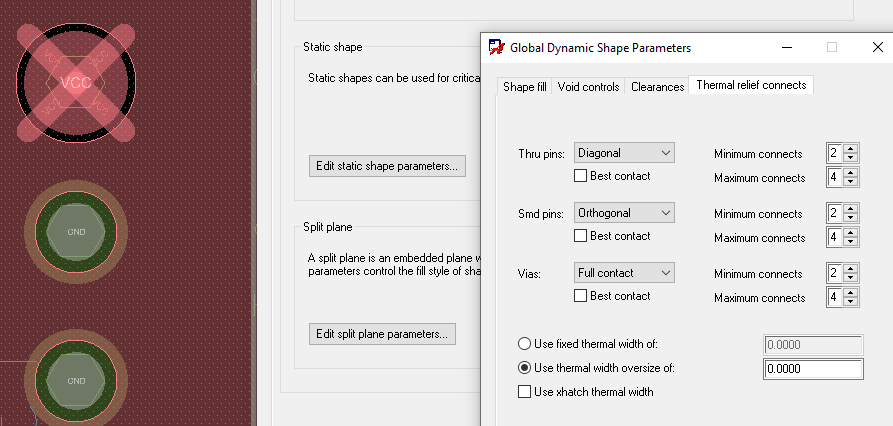

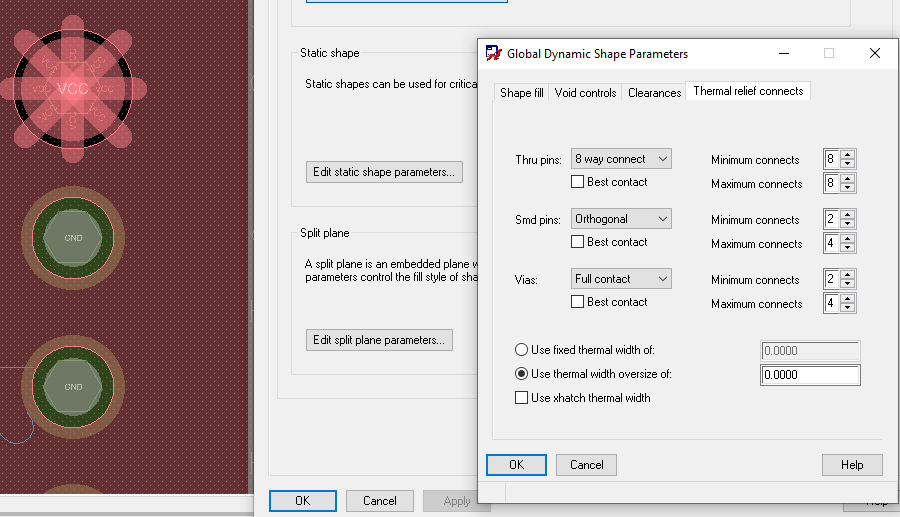

OrCAD Allegro PCB에서 Thermal Pad를 어떻게 연결할지에 대해 옵션을 선택할 수 있다.

1. 수직으로 연결

2. 대각선으로 연결

3. 통체로 연결 (일체화)

4. 8개의 통로로 연결

5. 연결 안함