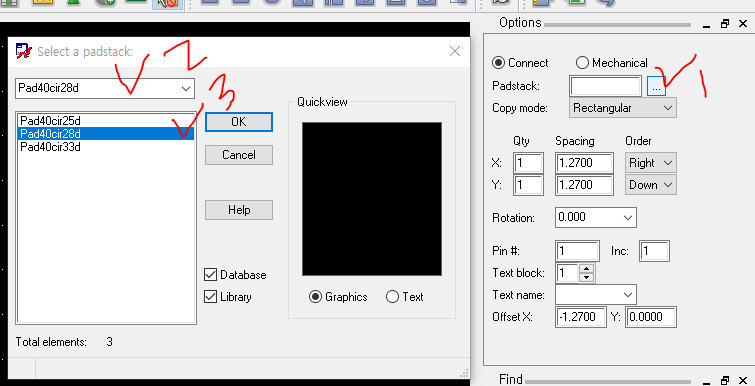

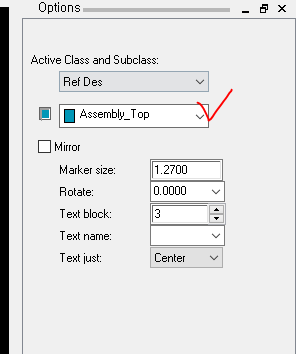

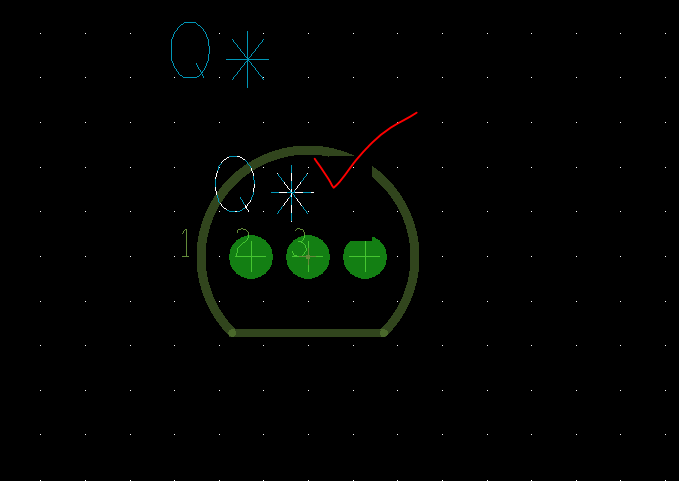

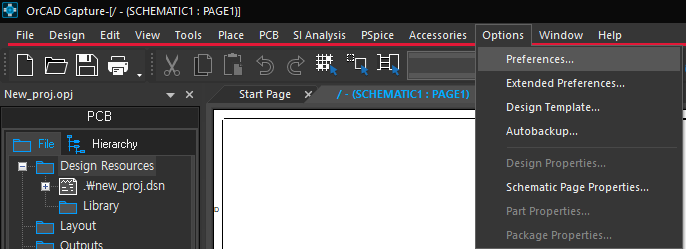

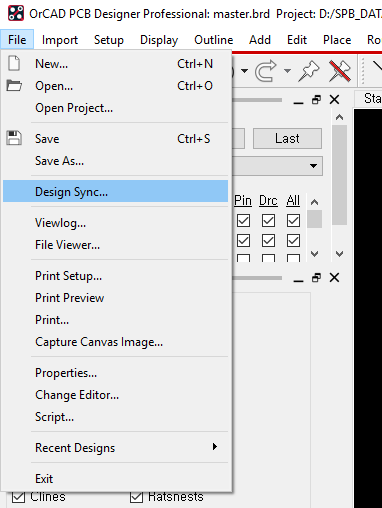

1. Faraday Cage (페러데이 새장)

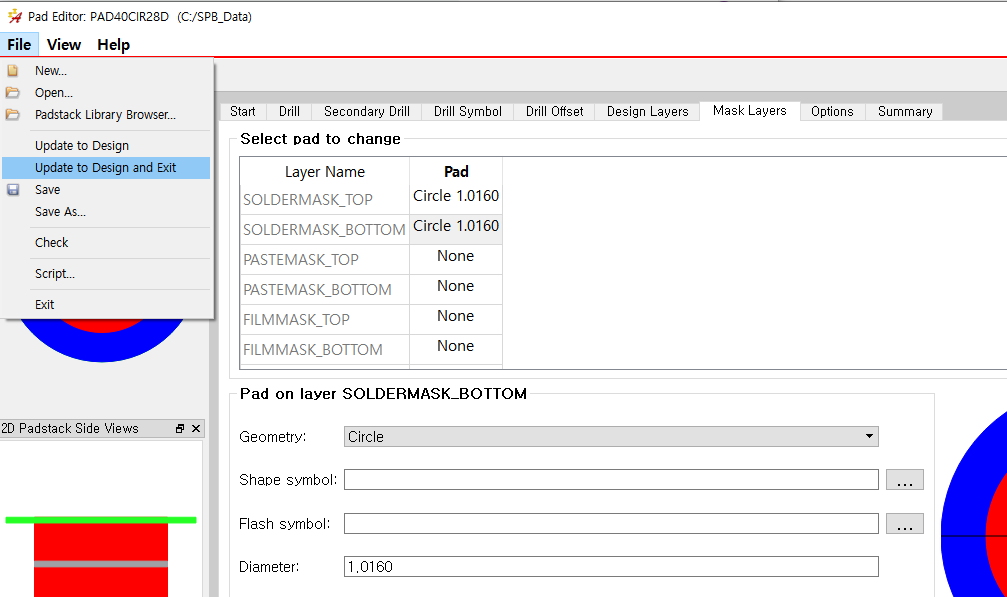

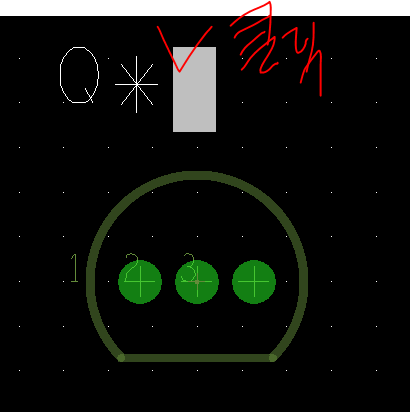

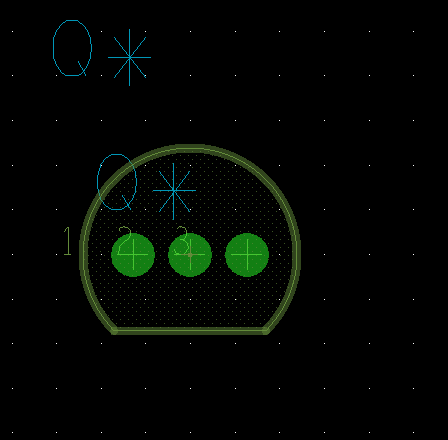

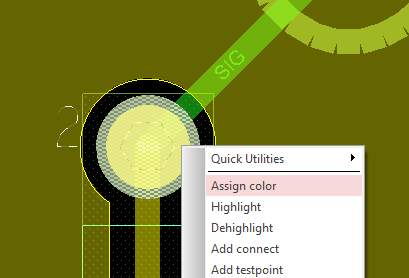

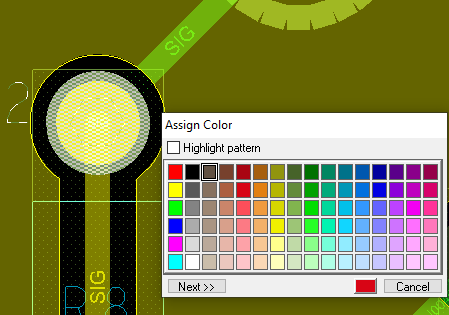

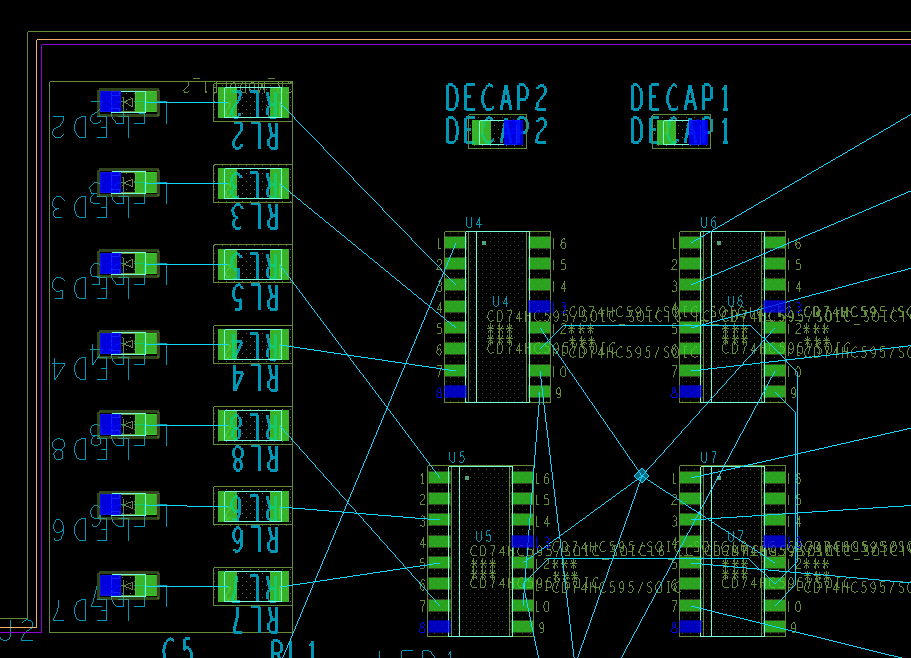

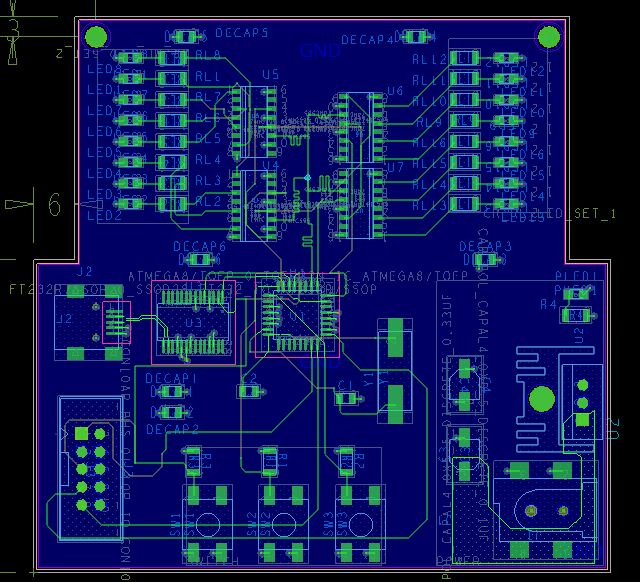

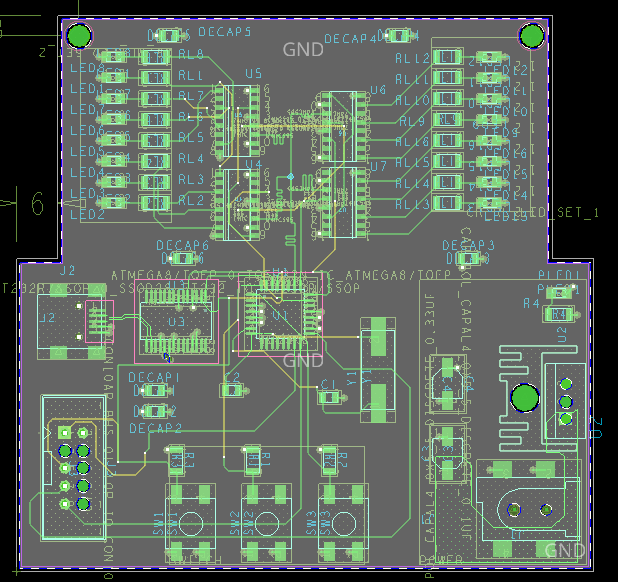

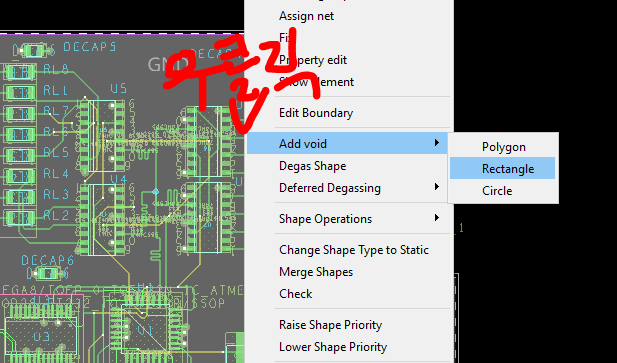

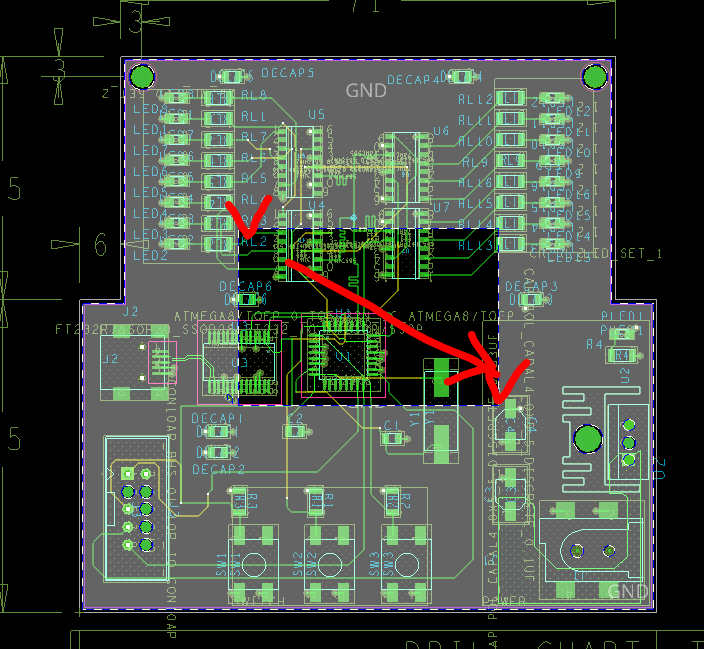

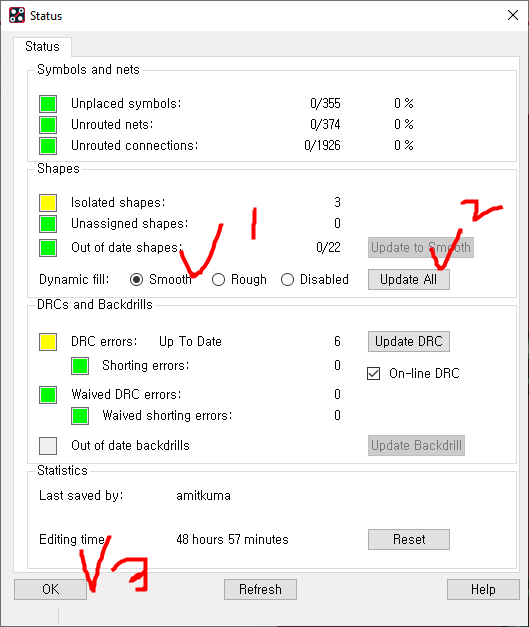

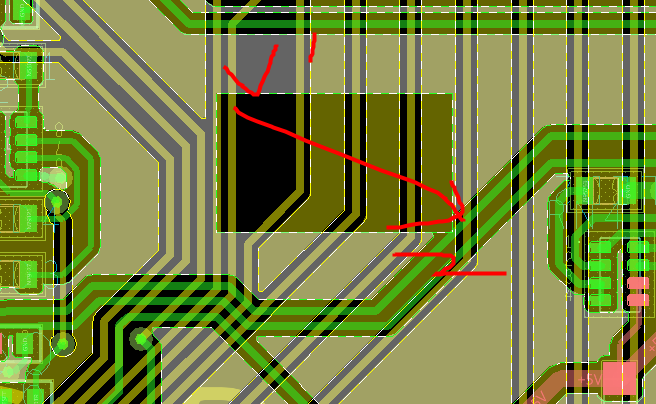

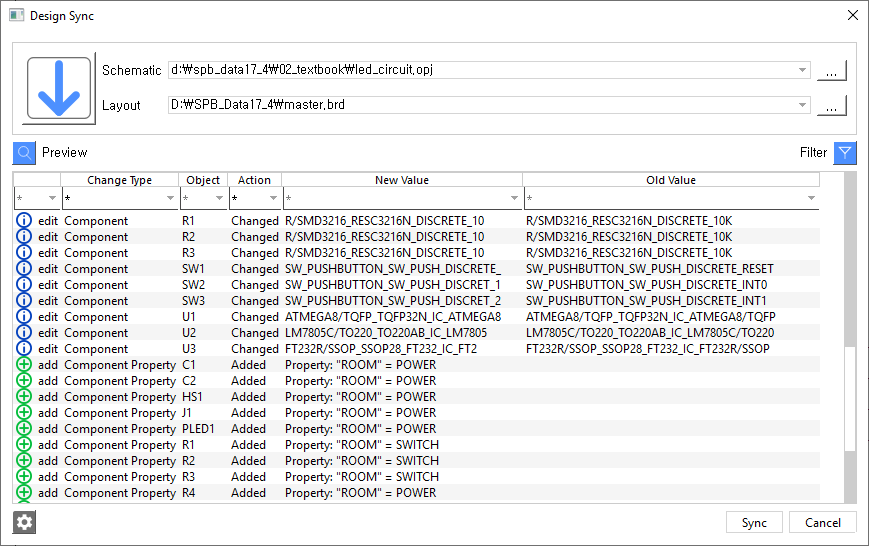

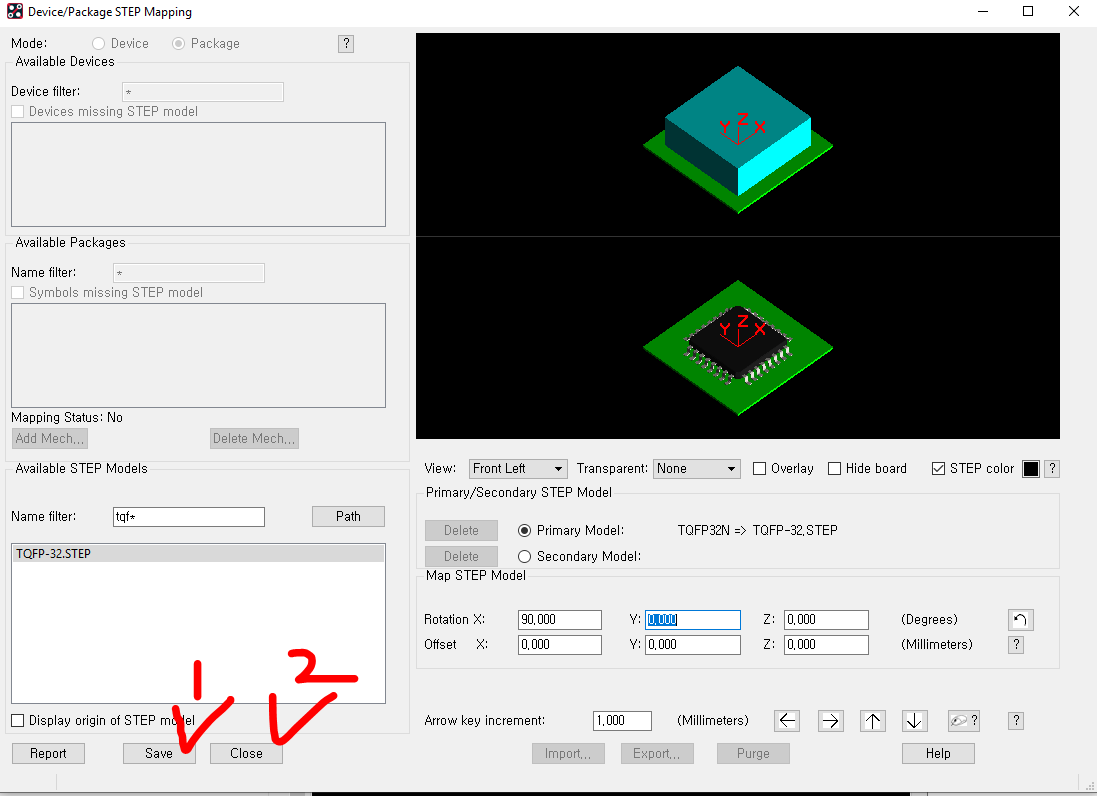

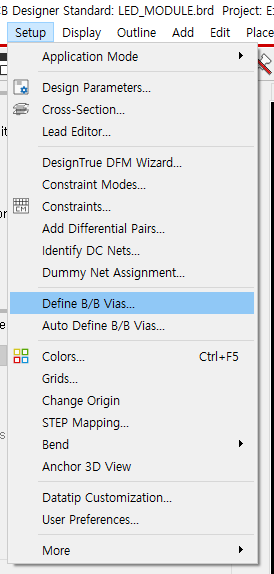

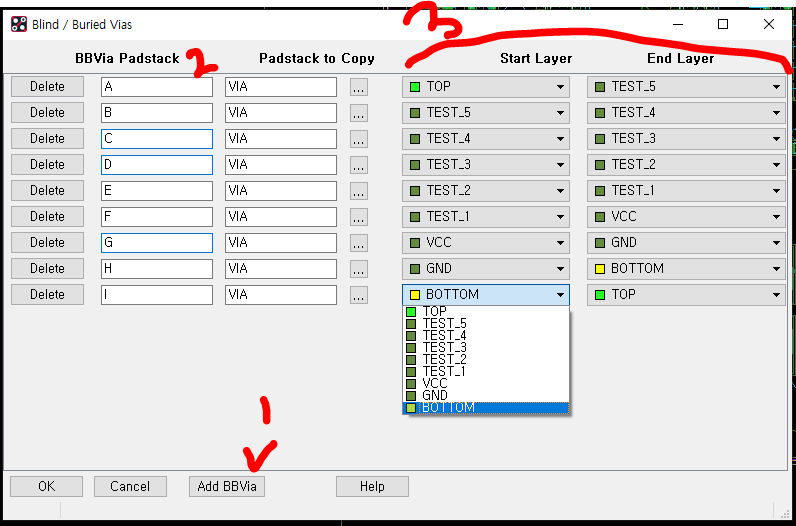

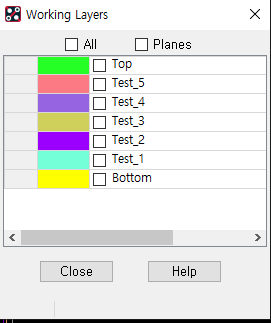

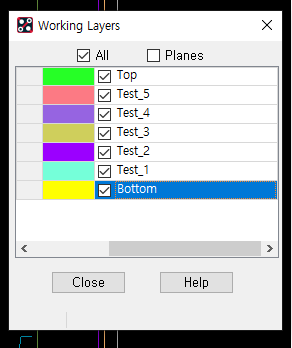

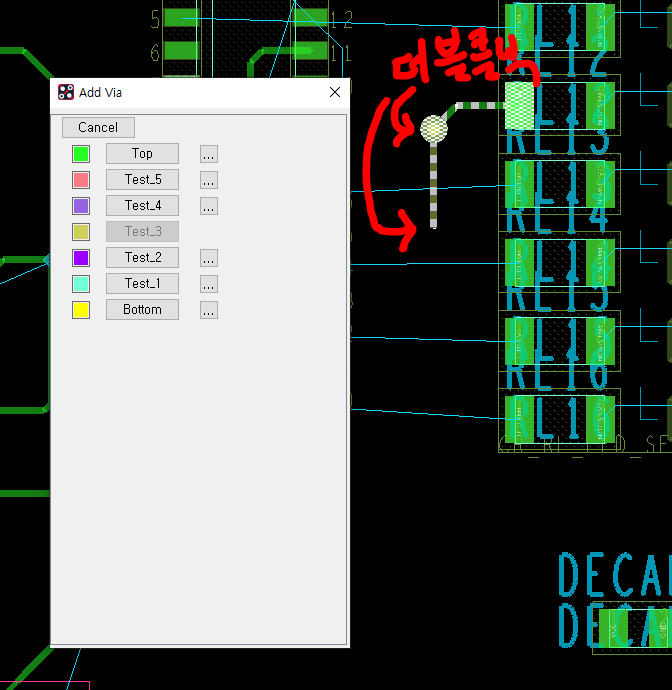

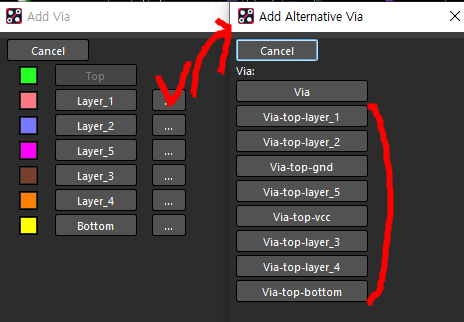

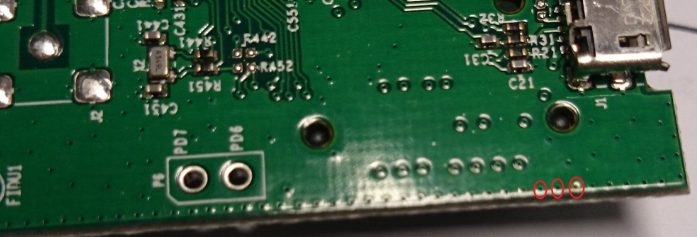

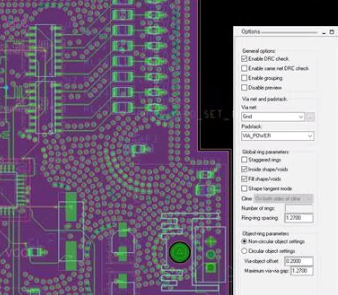

PCB를 보면 아래와 같은 기판을 본적이 있을 것이다. 외곽선을 따라 via홀이 쭉 뚫려 있는 것이다.

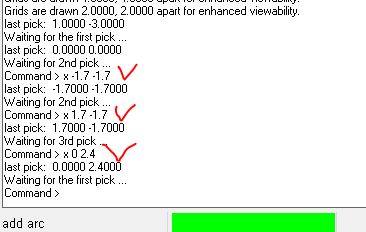

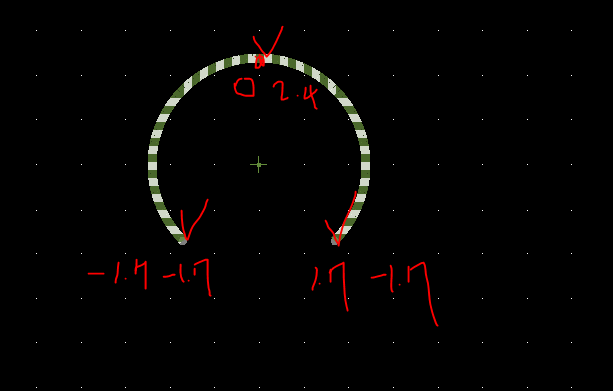

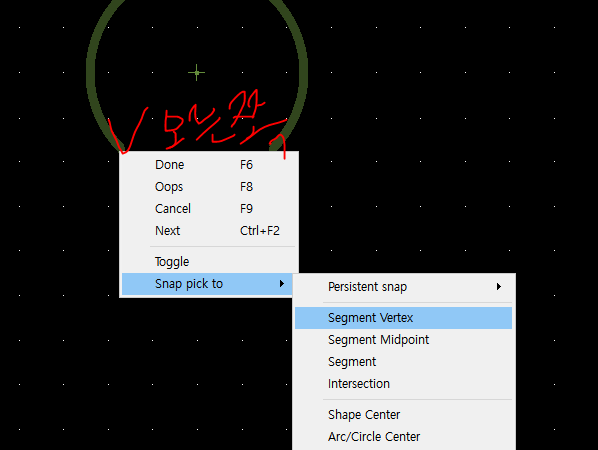

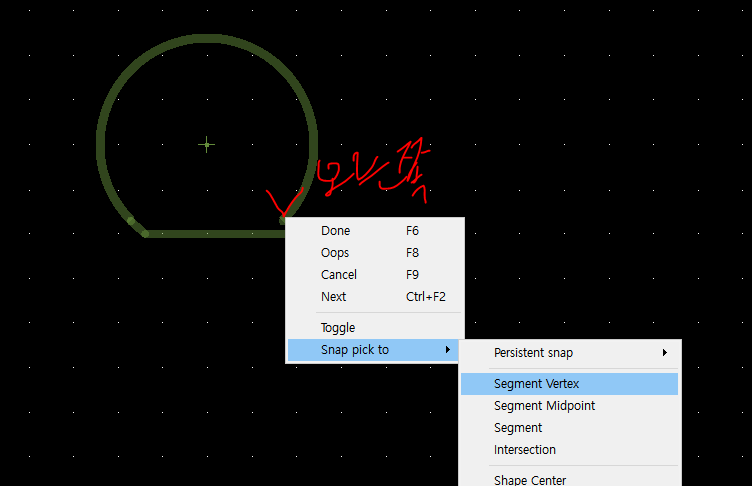

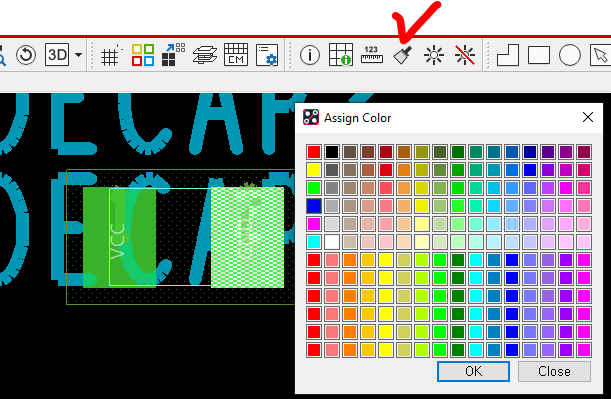

저렇게 외곽을 따라 via를 일정한 간격으로 뚫어놓은 이유는 아래와 같다. via 내측의 GND와 연결되어있다.

1) ESD(Electro Static Discharge) 정전기로 부터 회로를 보호, 외곽의 Cage에 발생한 정전기는 바로 via를 통해

GND로 접지시켜 흘러보냄

2) PCB edge로 방사되는 Radiated Emissions(RE) 대체적으로 감소시켜준다. (항상감소는 아님)

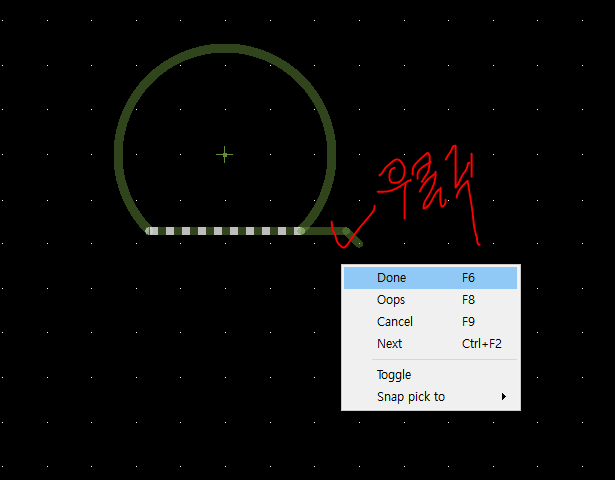

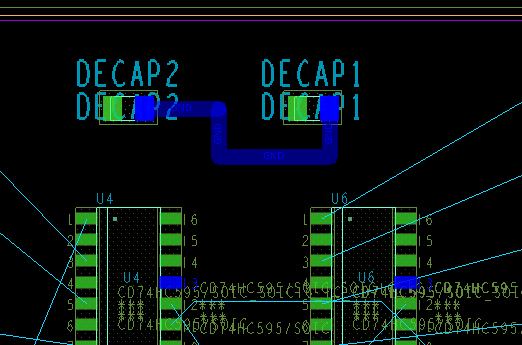

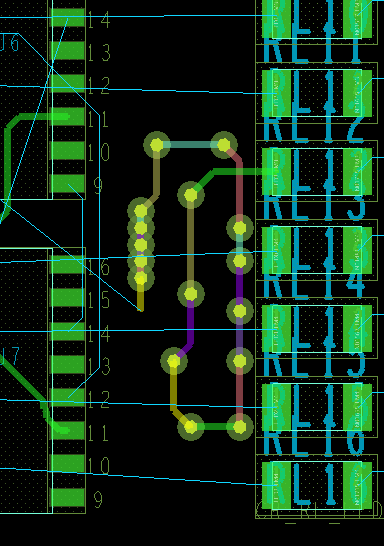

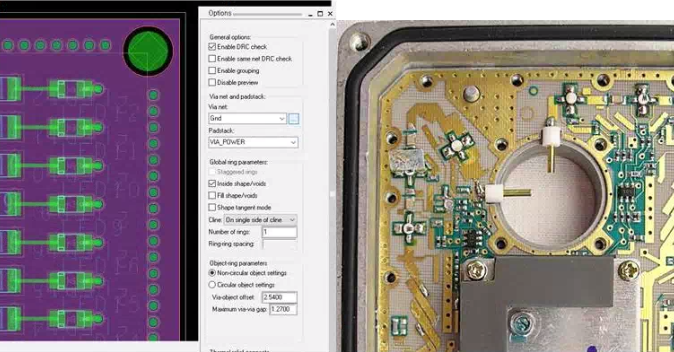

But) 공진주파수 영역에서 RE가 발생할 수 있다 => via들을 trace로 연결하여 해결(오른쪽 사진처럼)

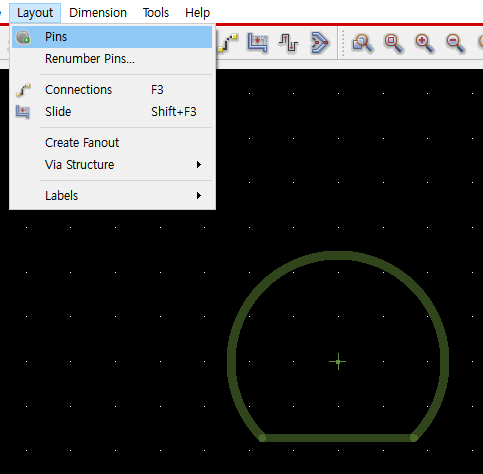

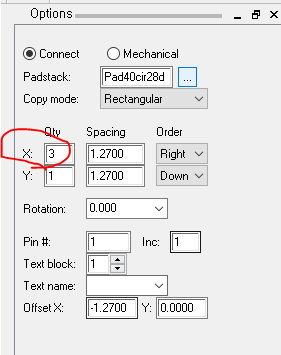

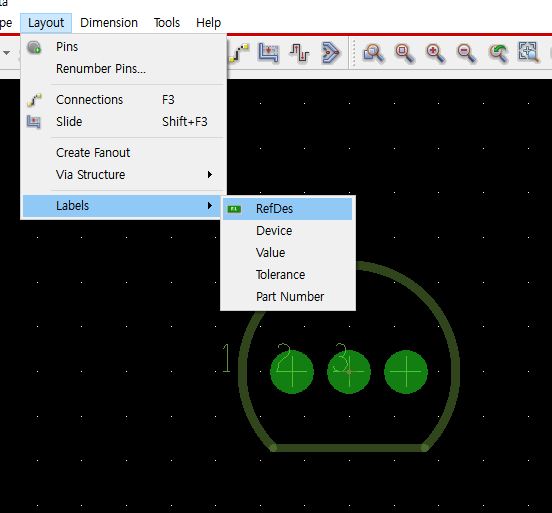

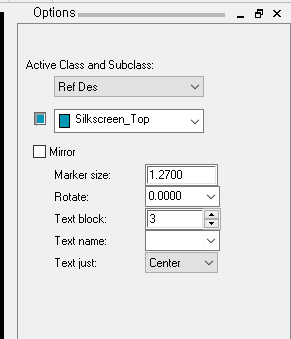

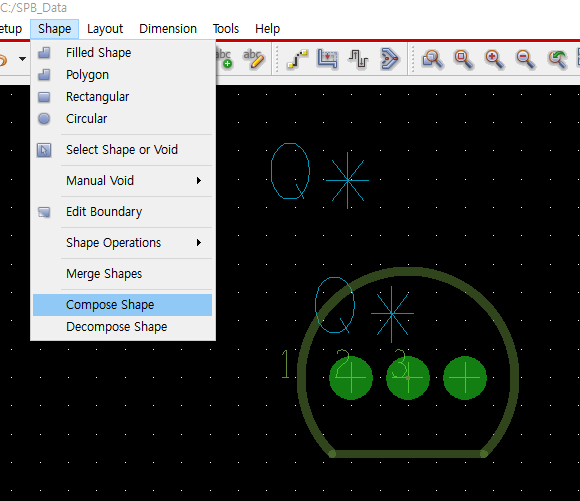

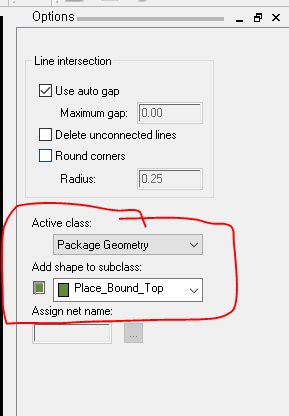

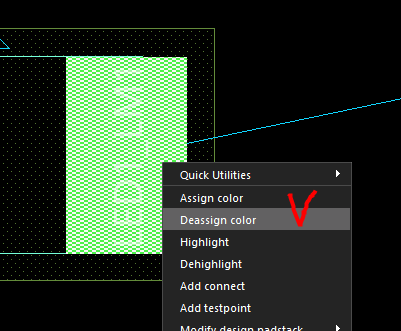

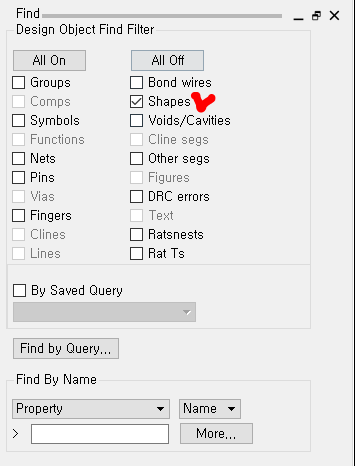

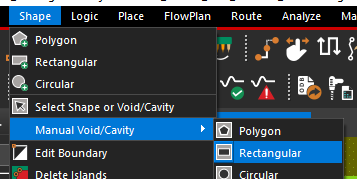

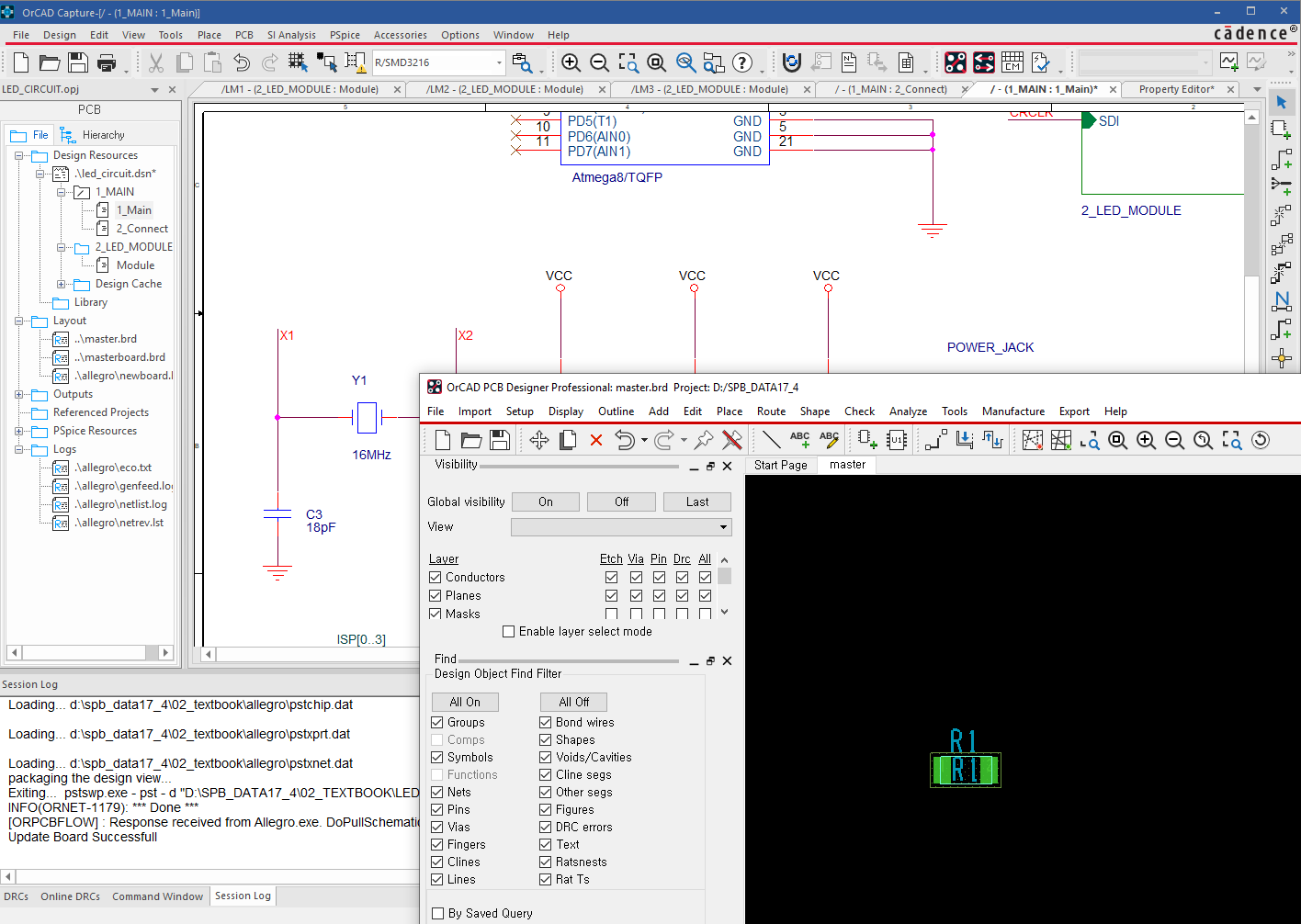

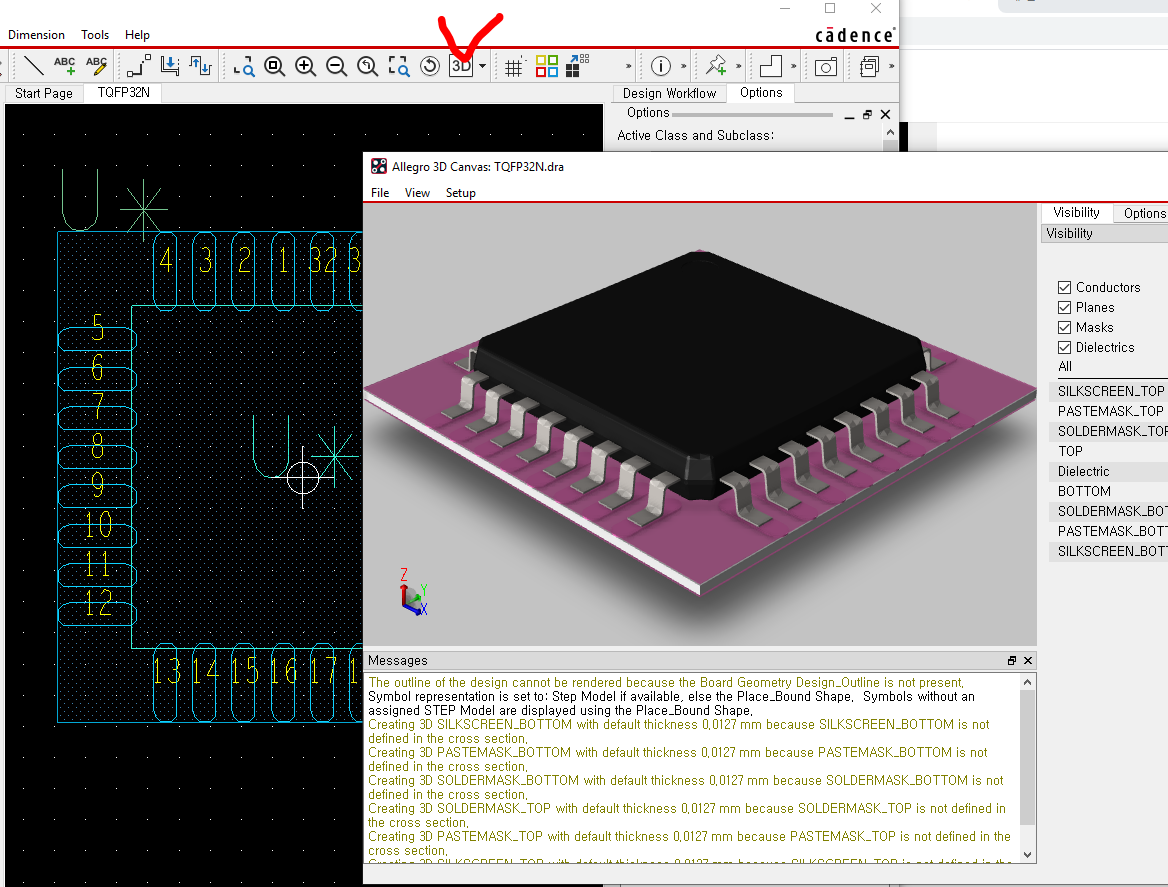

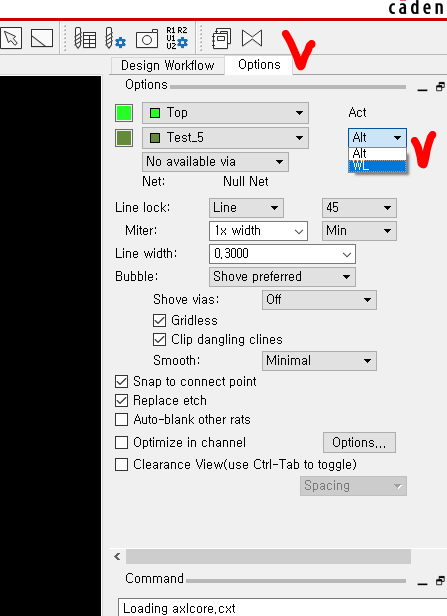

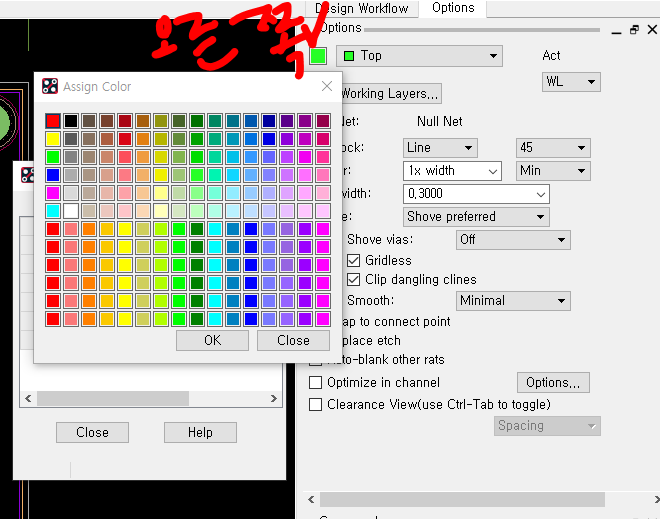

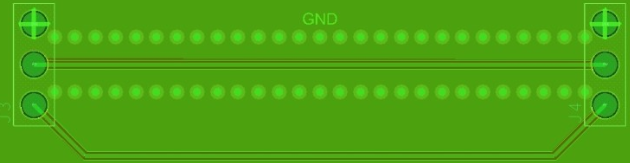

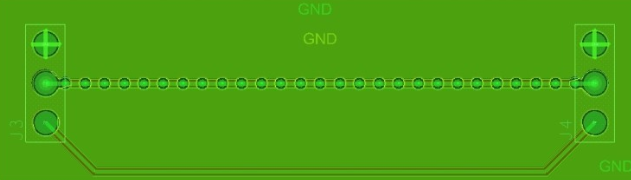

2. Trace를 따라 주변에 via배치 또는 Trace 위에 배치

1) 오실레이터의 Clock신호, 고속신호 송신을 위한 Differential Pair같은 Trace의 신호 보호

2) 방사되는 EMI 감소를 위함

3) Crosstalk을 막아주는 효과

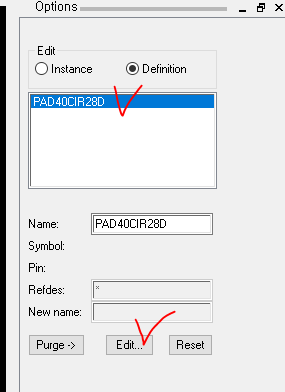

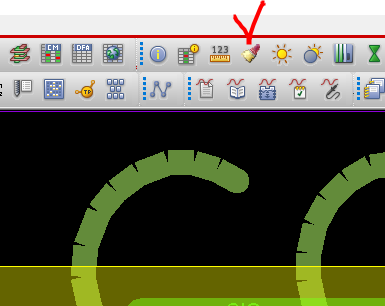

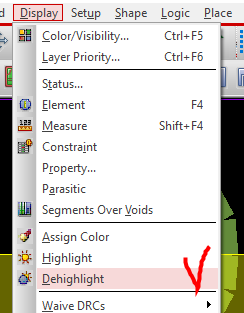

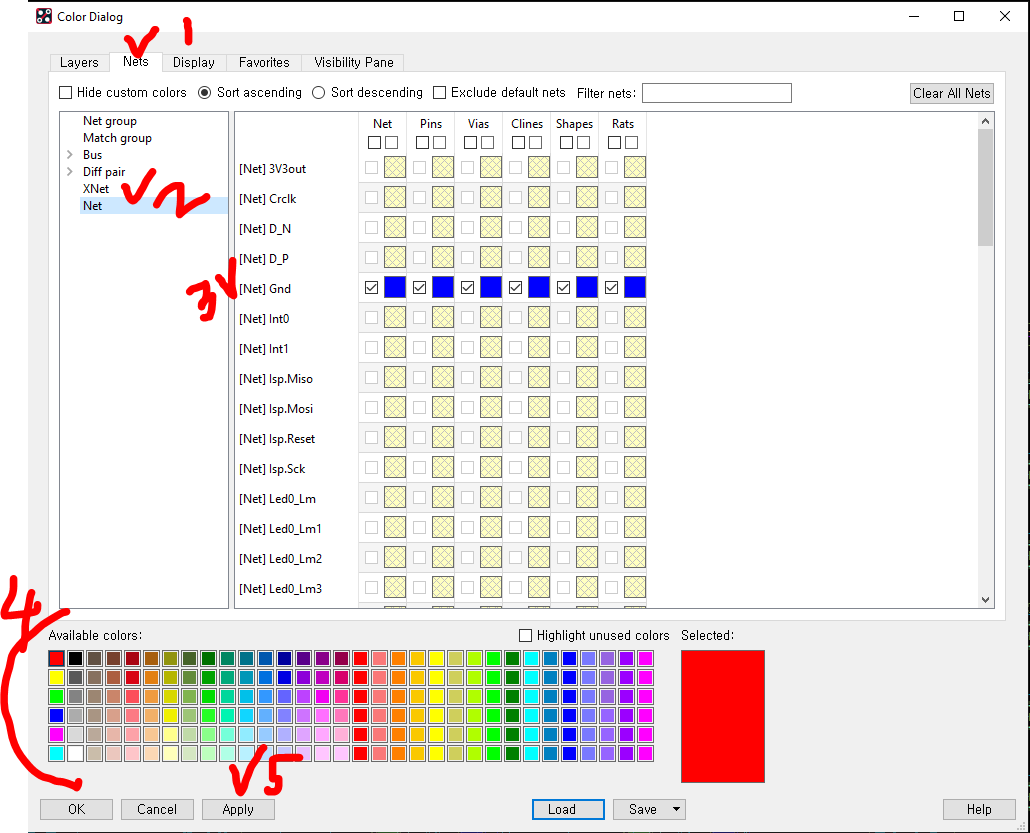

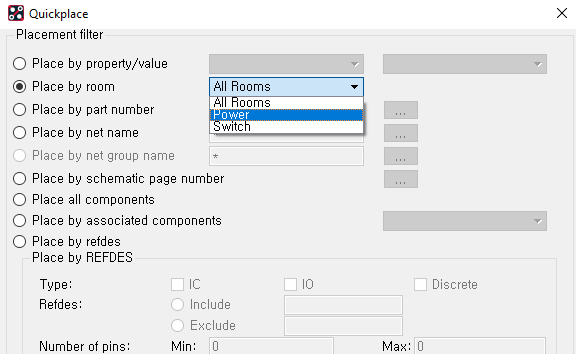

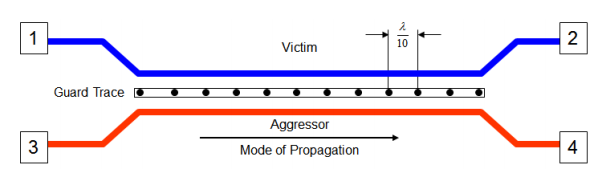

가드 트레이스 적용 유무와 사용 시 최적화

위 그림은 강하게 커플된 마이크로스트립(microstrip)에서 전형적인 NEXT와 FEXT를 보여준다. 가드 트레이스 통상 aggressor와 victim 사이이 패턴 폭 만큼의 spacing을 유지하며 삽입된다. 따라서 victim과 agg..

pcbee.tistory.com

1) Guard Trace 기능. (Cross Talk 감소효과)

2) EMI 감소기능

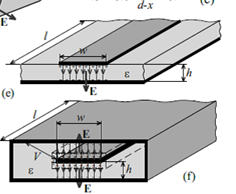

but) Microstrip보다는 Strip이 더 효과적이다.

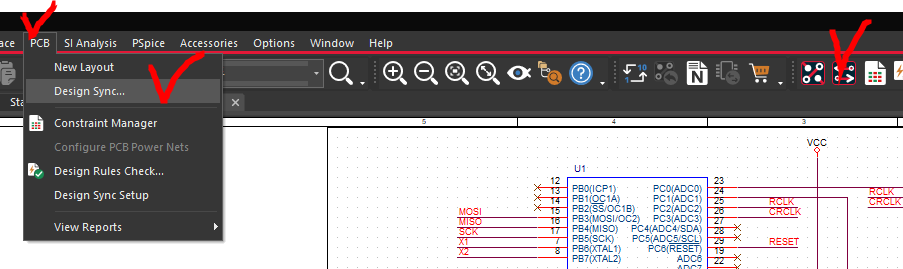

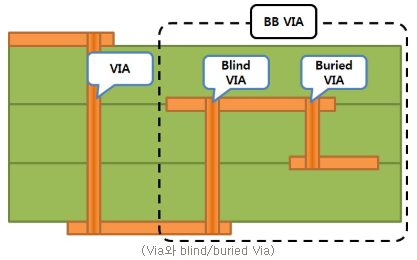

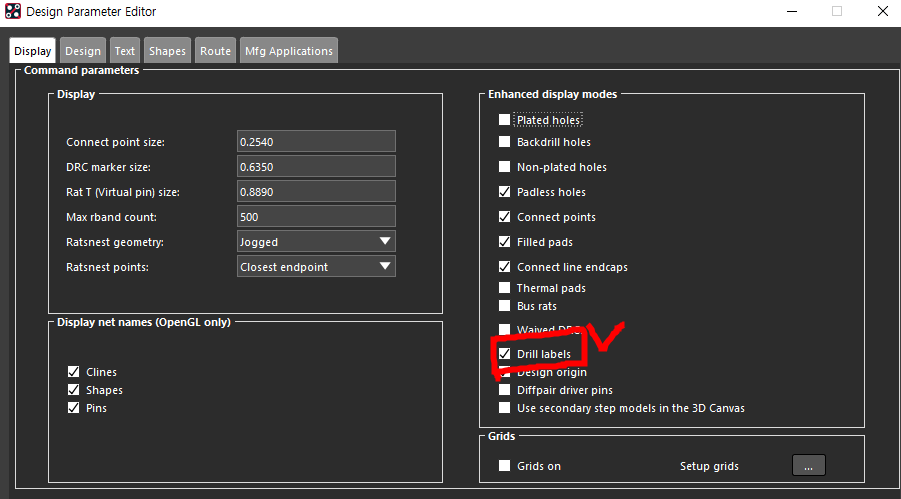

3. Board 전체에 via 배치

1) 전반적이 RE 감소.

2) Mode Frequency (공진이 발생할 수 있는 주파수) 조절

3) 대체로 6mm~10mm max 3cm 정도 간격으로 뚫어주면 효과 (1~10GHz 주파수의 board)

'전기전자공부 관련' 카테고리의 다른 글

| PCB Gerber file 포맷 'Gerber RS274X'에 대해서 (0) | 2020.03.25 |

|---|---|

| PCB에서 맨하탄/맨해튼 거리란? (Manhattan Distance) (0) | 2020.03.12 |

| 전기 전자 관련 용어 정리 (0) | 2020.01.22 |

| 특성임피던스 50옴을 쓰는 이유? (0) | 2020.01.17 |

| EMI/EMC 전자파 방출을 고려한 PCB설계시 중요 Tip (0) | 2019.12.26 |